# DINAMAP™ *PLUS*Vital Signs Monitor

Service Manual

CRITIKON

a Johnson-Johnson company

### LIST OF EFFECTIVE PAGES

Part No./Rev. Page No. Date of Latest Revision 776532PA All Original (May 1992)

U.S. Patent 4,349,034 U.S. Patent 4,360,029 U.S. Patent 4,501,280 U.S. Patent 4,546,775 Patent Pending

**CAUTION:** Federal (U.S.A.) law restricts this device to sale by or on the order of a health care practitioner.

The content of this document including all figures and drawings is proprietary information of CRITIKON, INC., provided solely for purposes of operation, maintenance or repair, and dissemination for other purposes or publication or copying thereof is prohibited without prior written consent by CRITIKON, INC., Tampa, Fla.

Photographs may show design models; production units may incorporate changes.

© 1992 Critikon, Inc. All rights reserved. Printed in U.S.A.

| SECTION 1.   | 1.1      | Scope of Manual                | 1-1  |

|--------------|----------|--------------------------------|------|

| INTRODUCTION | 1.2      | Manual Changes                 | 1-2  |

|              | 1.3      | Service Policy                 | 1-2  |

|              | 1.3.1    | Technical Assistance           | 1-3  |

|              | 1.3.1.1  | Via Phone                      | 1-3  |

|              | 1.3.1.2  | Via FAX                        | 1-4  |

|              | 1.3.2    | Repair Service                 | 1-4  |

|              | 1.3.3    | Repair Parts                   | 1-5  |

|              | 1.4      | Product Description            | 1-5  |

|              | 1.4.1    | General Description            | 1-5  |

|              | 1.4.2    | Physical Description           | 1-6  |

|              | 1.4.3    | Storage Batteries              | 1-6  |

| • • •        | 1.4.4    | Product Reorder Information    | 1-8  |

|              | 1.4.5    | Accessory Reorder Information  | 1-8  |

|              | 1.4.5.1  | Critikon Accessories           | 1-8  |

|              | 1.4.5.2  | After-Market Accessories       | 1-10 |

|              | 1.4.6    | Specifications                 | 1-10 |

|              | 2.1      | Introduction                   | 2-1  |

| SECTION 2.   | 2.2      | System Theory of Operation     | 2-1  |

| THEORY OF    | 2.3      | Functional Theory of Operation | 2-3  |

| OPERATION    | 2.3.1    | System Processor               | 2-3  |

|              | 2.3.2    | Data Acquisition System        | 2-4  |

|              | 2.3.3    | Pulse Oximetry System          | 2-6  |

|              | 2.3.4    | NIBP System                    | 2-7  |

|              | 2.3.5    | Pneumatics System              | 2-8  |

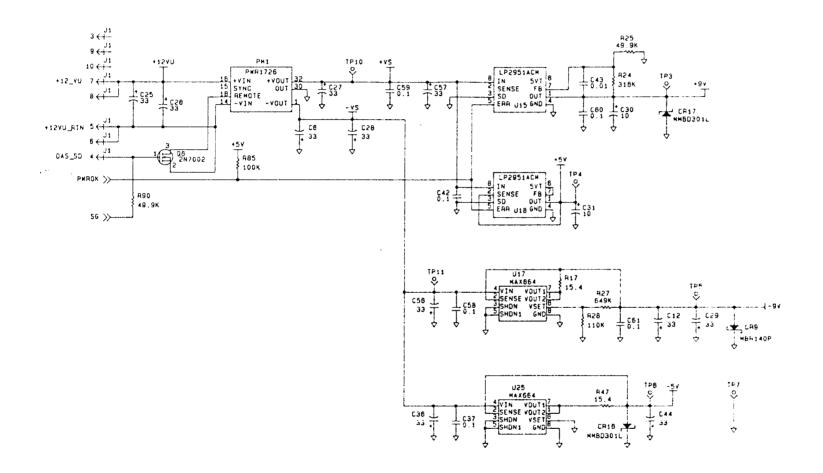

|              | 2.3.6    | Power Supply                   | 2-10 |

|              | 2.4      | Schematic Descriptions         | 2-13 |

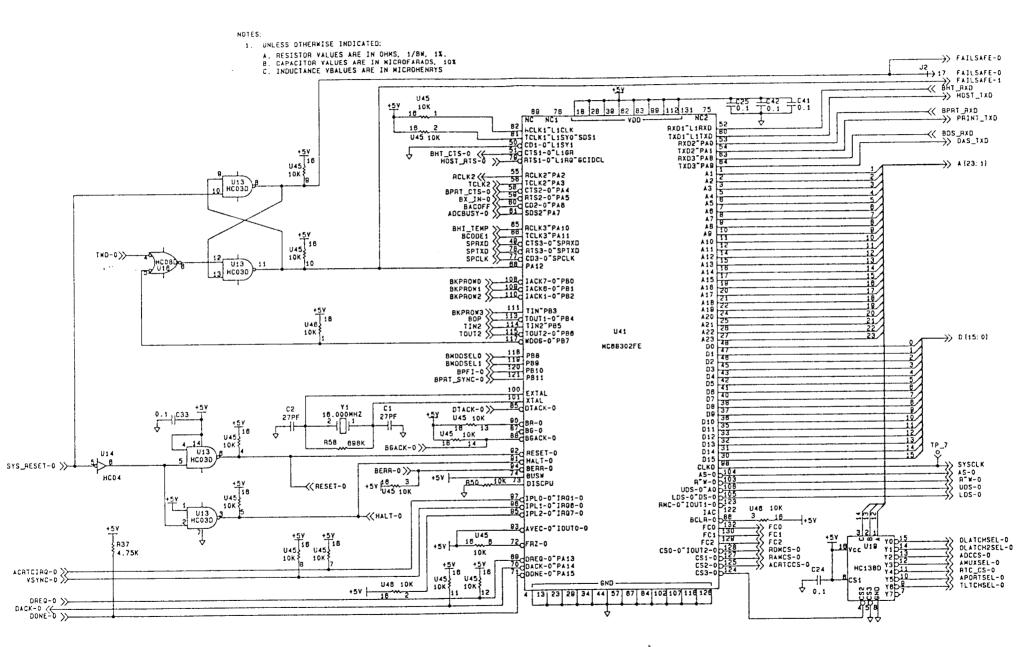

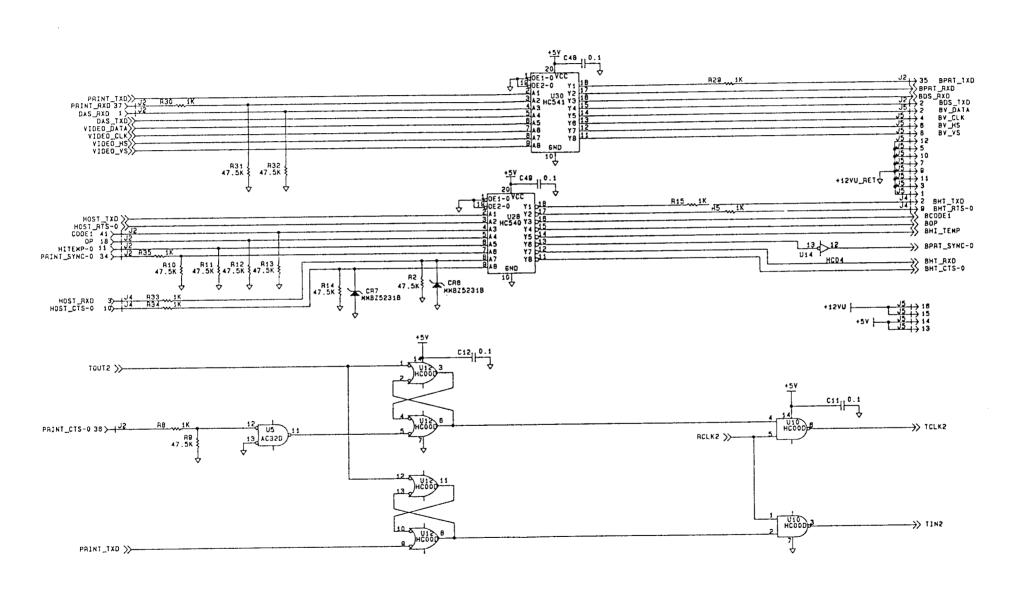

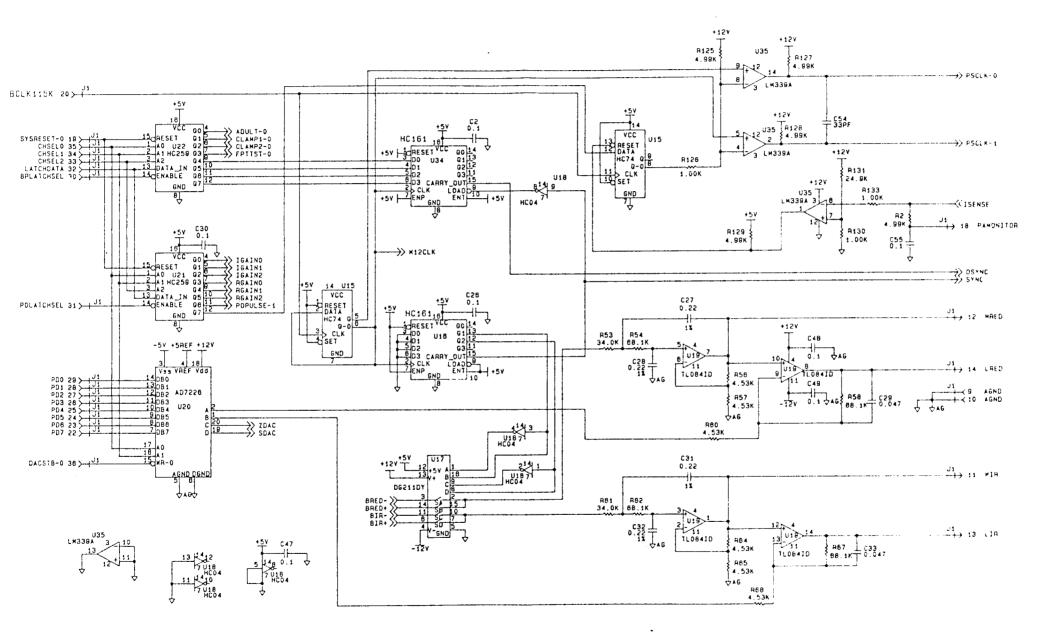

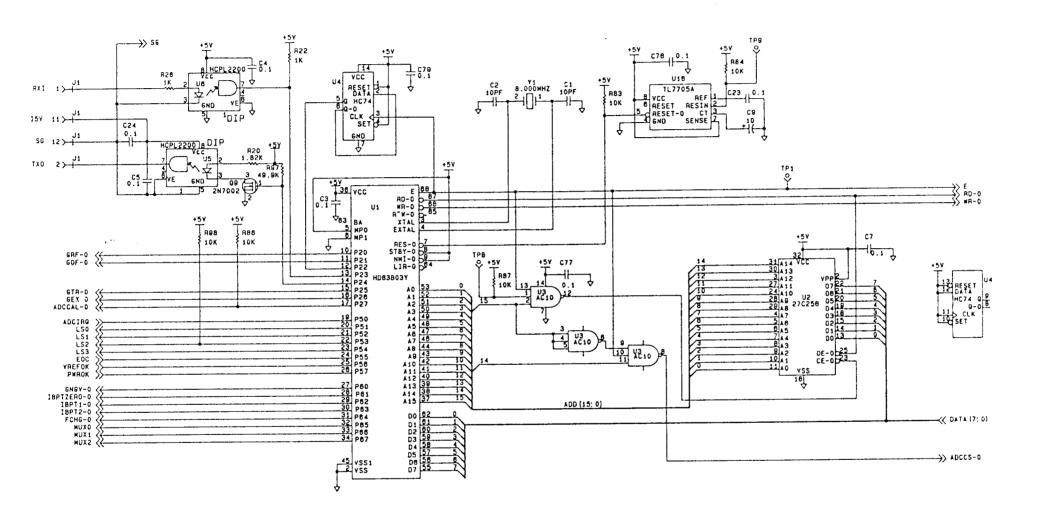

|              | 2.4.1    | System Processor Board         | 2-13 |

|              | 2.4.1.1  | Failsafe Logic                 | 2-15 |

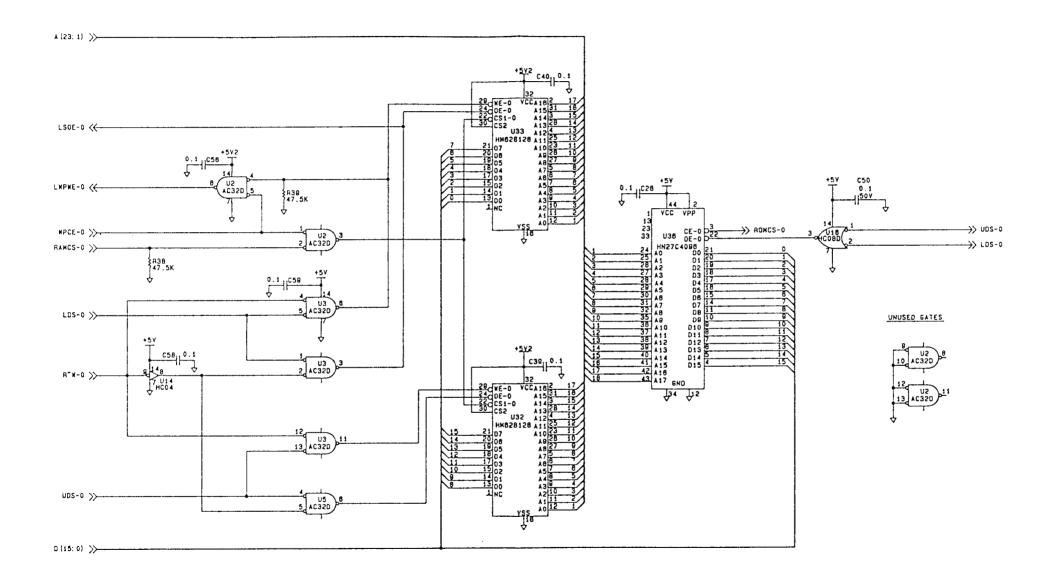

|              | 2.4.1.2  | Read-Only Memory               | 2-16 |

|              | 2.4.1.3  | Read/Write Memory              | 2-17 |

|              | 2.4.1.4  | Serial EEPROM                  | 2-17 |

|              | 2.4.1.5  | Analog Input Subsystem         | 2-18 |

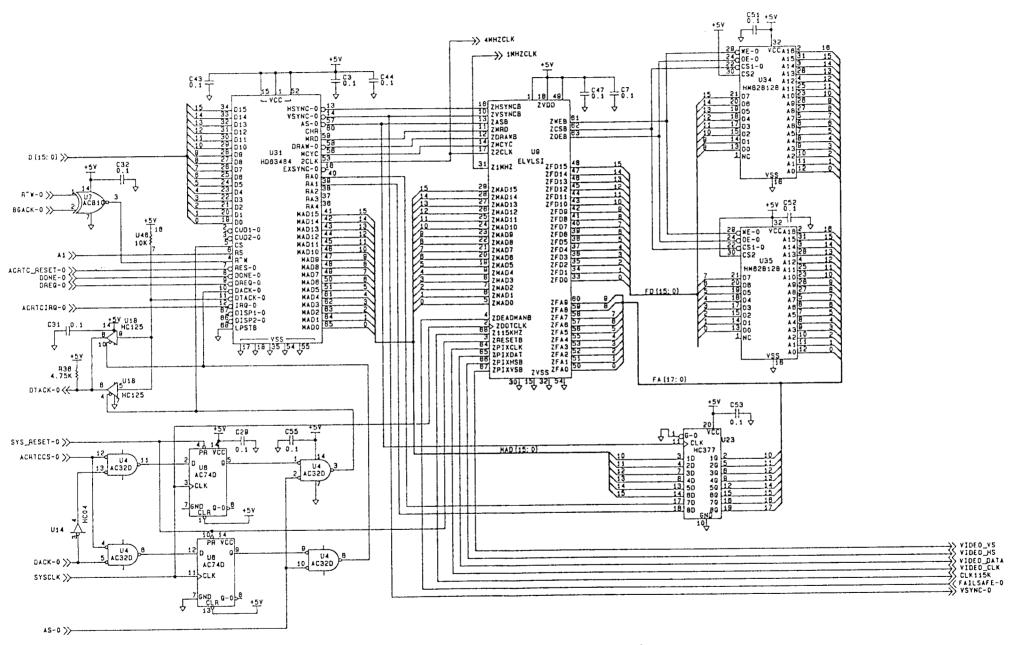

|              | 2.4.1.6  | Graphics Subsystem             | 2-19 |

|              | 2.4.1.7  | Realtime Clock                 | 2-20 |

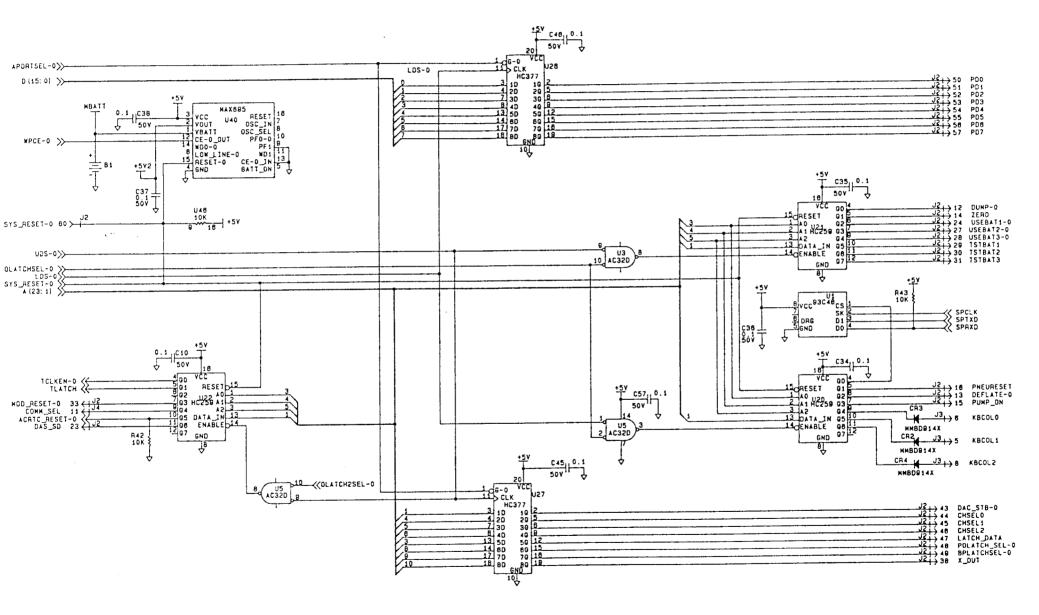

|              | 2.4.1.8  | Audio Subsystem                | 2-20 |

|              | 2.4.1.9  | Keypad Interface               | 2-22 |

|              | 2.4.1.10 | Digital Inputs                 | 2-22 |

|              | 2.4.1.11 | Digital Output Ports           | 2-22 |

CONTINUED

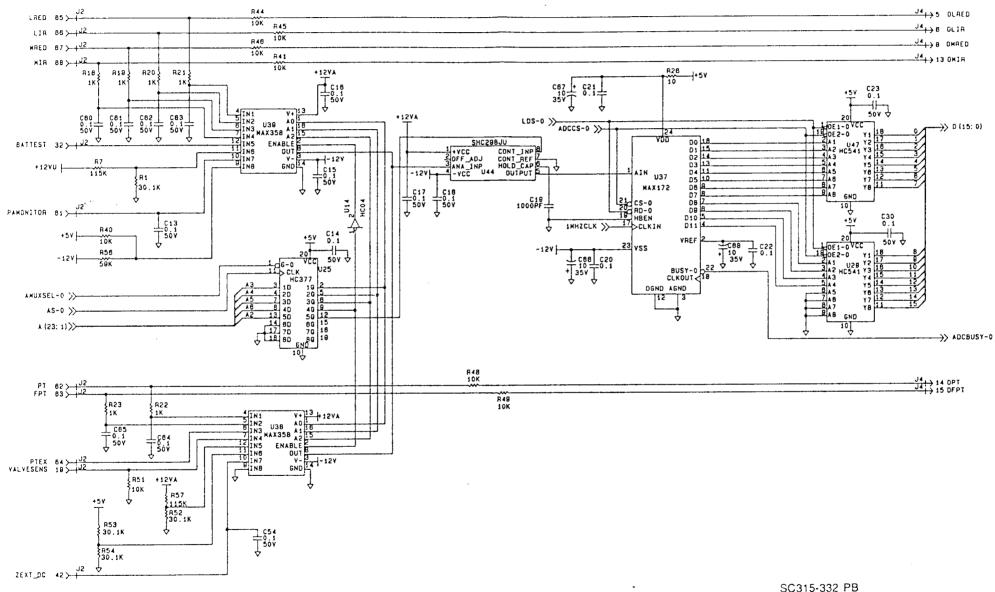

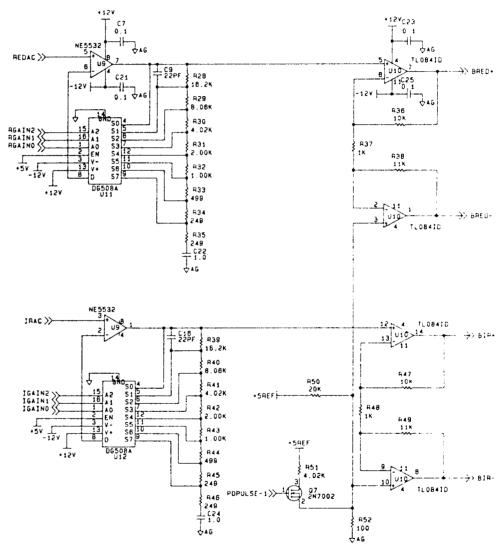

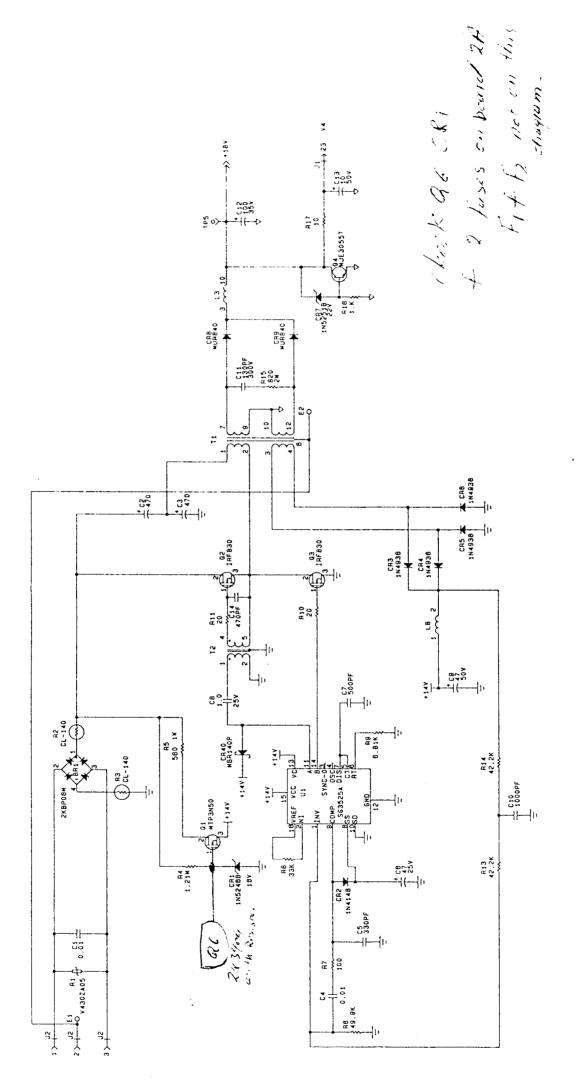

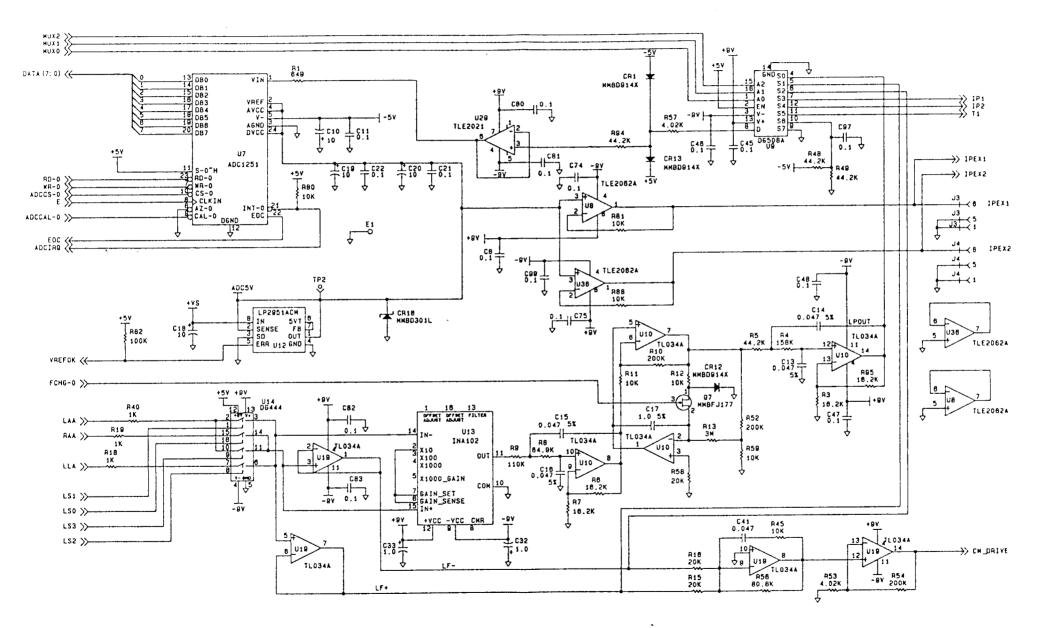

| SECTION 2. | 2.4.2    | DAS Board                         | 0.00 |

|------------|----------|-----------------------------------|------|

| THEORY OF  | 2.4.2.1  | DAS CPU, Opto-isolators, and      | 2-23 |

| OPERATION  |          | Control Logic                     | 2-24 |

| Continued  | 2.4.2.2  | Analog To Digital Converter and   |      |

|            |          | Multiplexer                       | 2-25 |

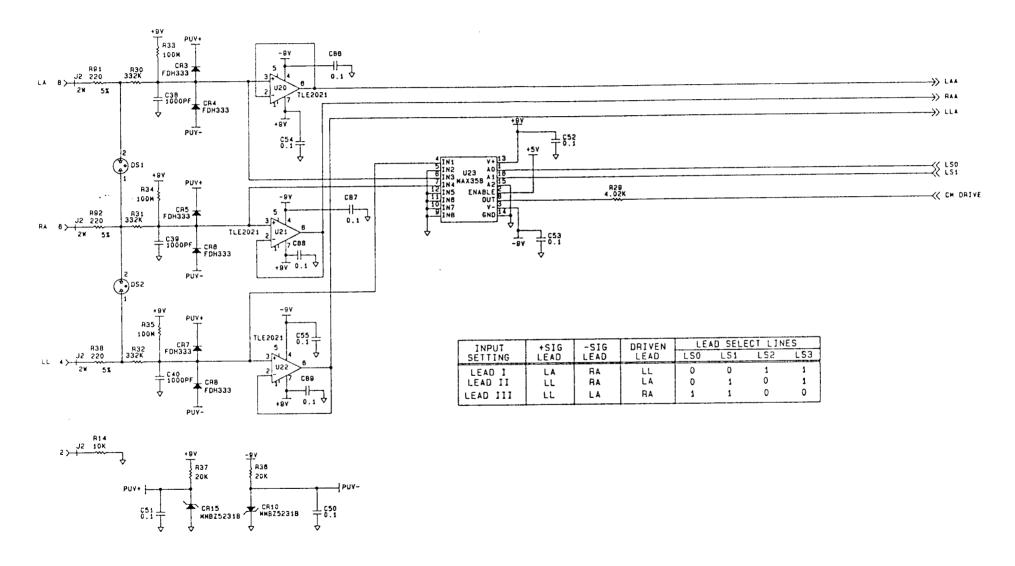

|            | 2.4.2.3  | ECG Channel and Lead Switching    | 2-26 |

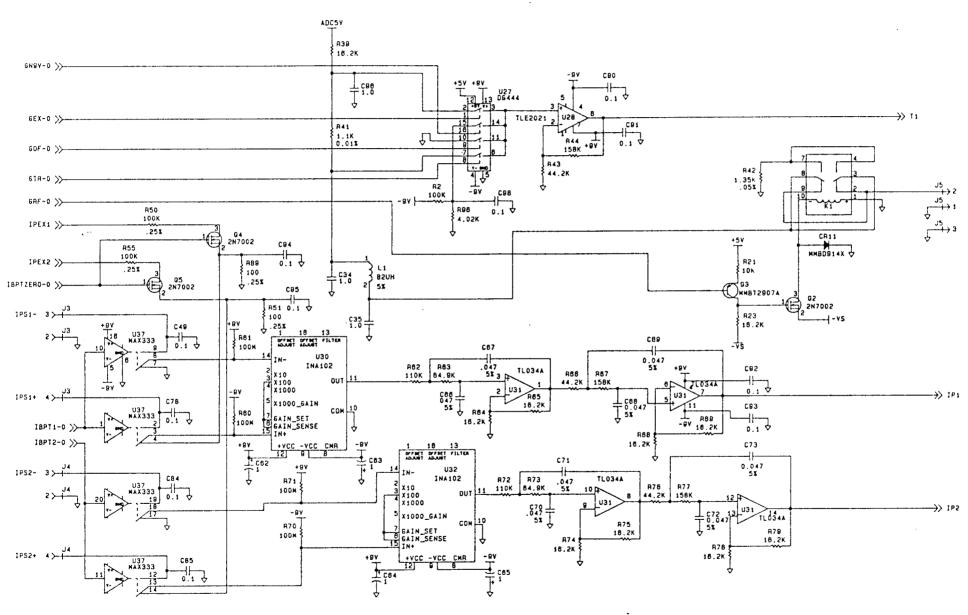

| •          | 2.4.2.4  | Invasive Pressure Channels        | 2-28 |

|            | 2.4.2.5  | Temperature Channel               | 2-29 |

|            | 2.4.2.6  | Isolated Power Supply             | 2-30 |

|            | 2.4.2.7  | Addressing                        | 2-31 |

|            | 2.4.2.8  | Port Assignments                  | 2-32 |

| ***        | 2.4.2.9  | A/D Converter                     | 2-35 |

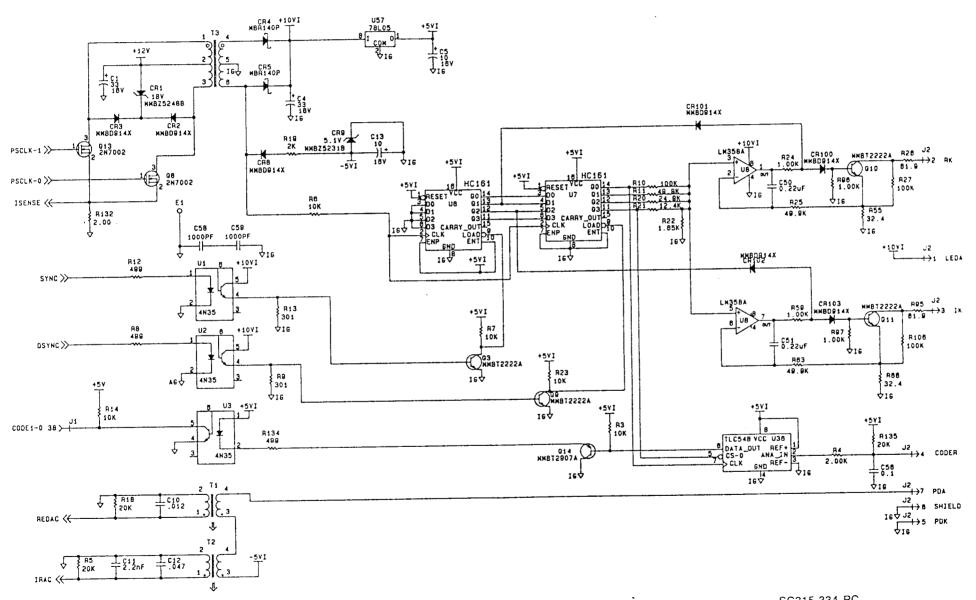

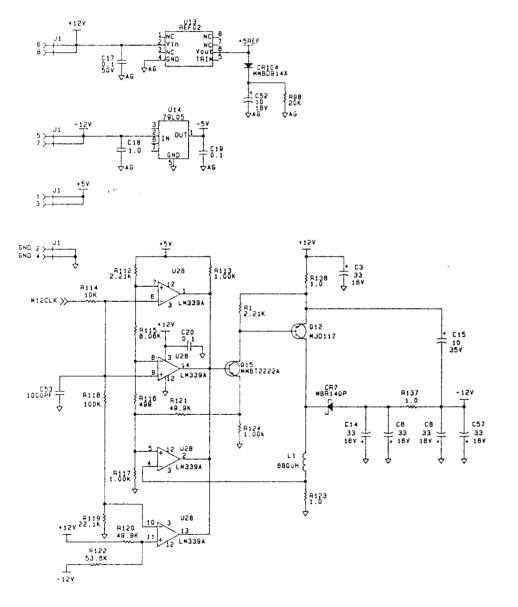

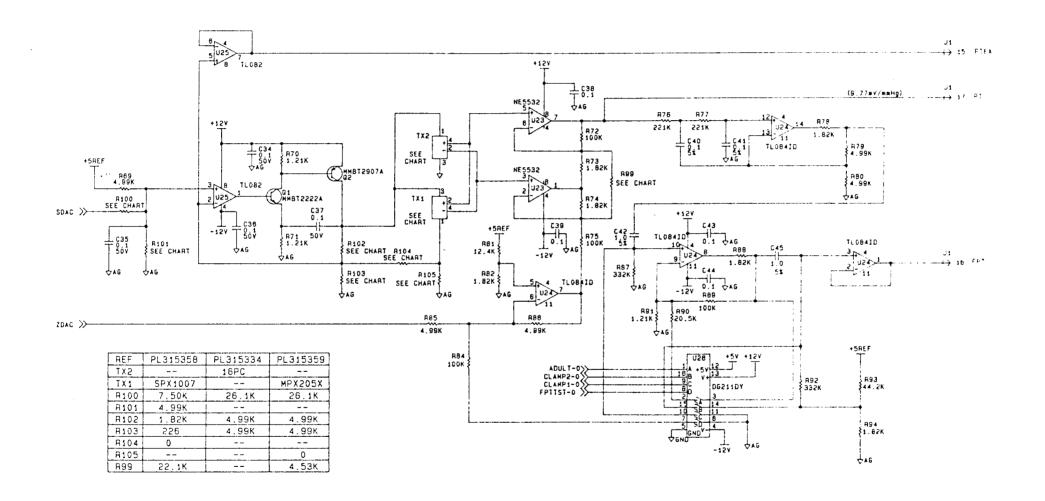

|            | 2.4.3    | Analog Board                      | 2-35 |

|            | 2.4.3.1  | Control Interface and DAC         | 2-36 |

|            | 2.4.3.2  | Clock Generator and Sync          | 2-36 |

|            | 2.4.3.3  | Negative 12 Volt Power Supply     | 2-38 |

|            | 2.4.3.4  | Isolated Power Supply             | 2-39 |

|            | 2.4.3.5  | LED Current Control               | 2-40 |

|            | 2.4.3.6  | Sensor Code Detection             | 2-41 |

|            | 2.4.3.7  | Sensor AC Amplifiers              | 2-42 |

|            | 2.4.3.8  | Synchronous Detectors and Filters | 2-43 |

|            | 2.4.3.9  | PO Pulse Amplifiers               | 2-43 |

|            | 2.4.3.10 | Pressure Transducer Excitation    | 2-44 |

| •          | 2.4.3.11 | Transducer Amplifier              | 2-44 |

|            | 2.4.3.12 | BP Pulse Amplifier and Clamp      | 2-45 |

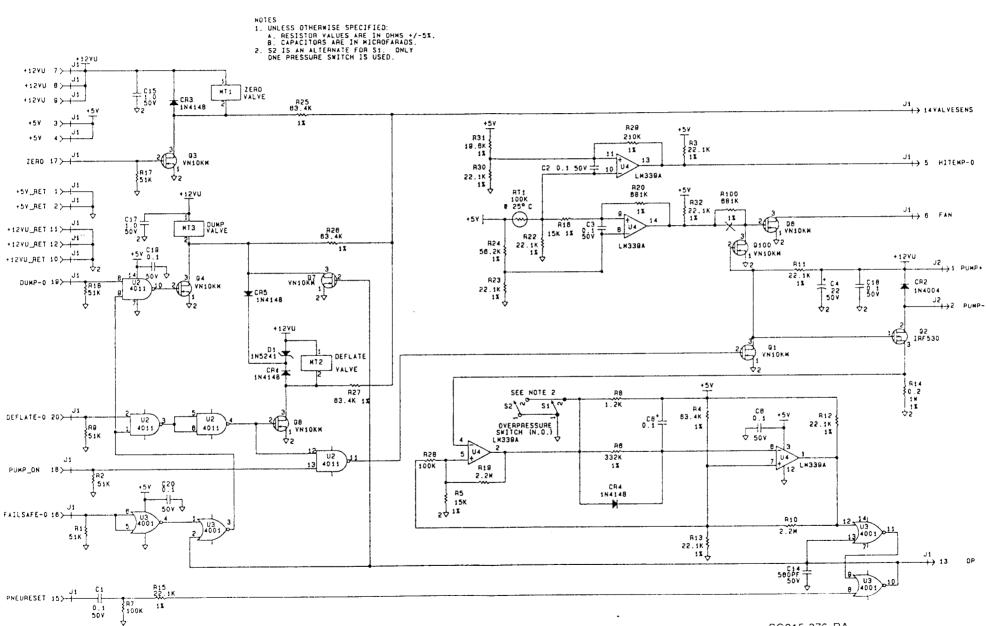

|            | 2.4.4    | Pneumatics Board                  | 2-45 |

|            | 2.4.4.1  | Valve Drive Circuit               | 2-45 |

|            | 2.4.4.2  | Pump Drive Circuit                | 2-46 |

|            | 2.4.4.3  | Overpressure Switch and Safety    |      |

|            | _        | Interlocks                        | 2-46 |

|            | 2.4.4.4  | Time Delay Circuit                | 2-47 |

|            | 2.4.4.5  | Thermal Switch Circuit            | 2-48 |

CONTINUED

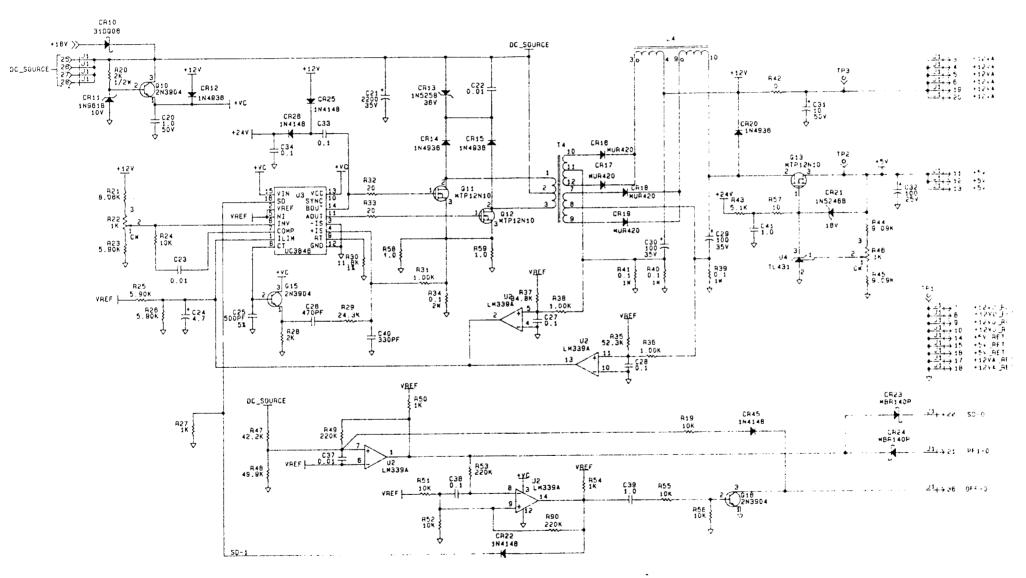

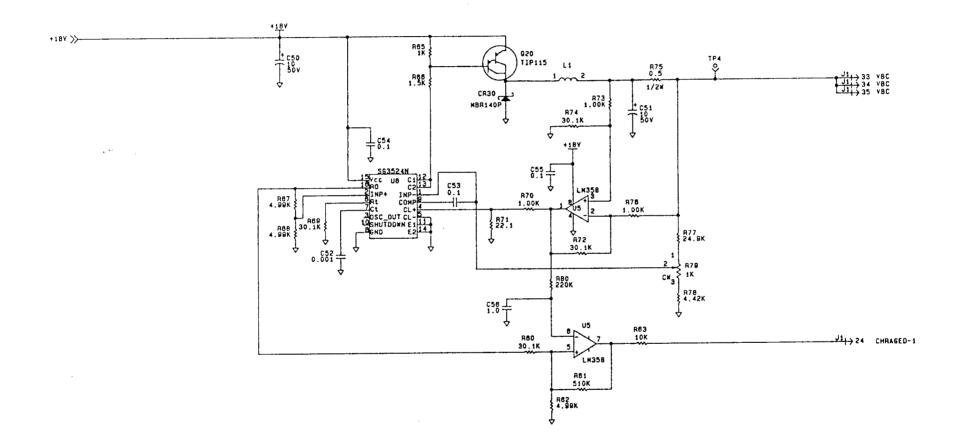

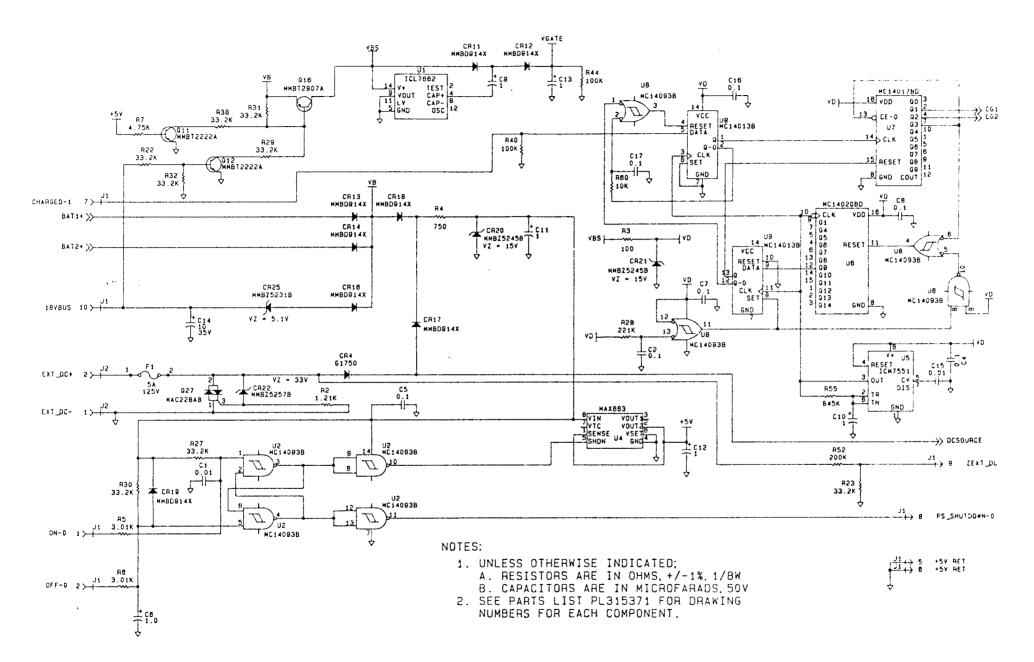

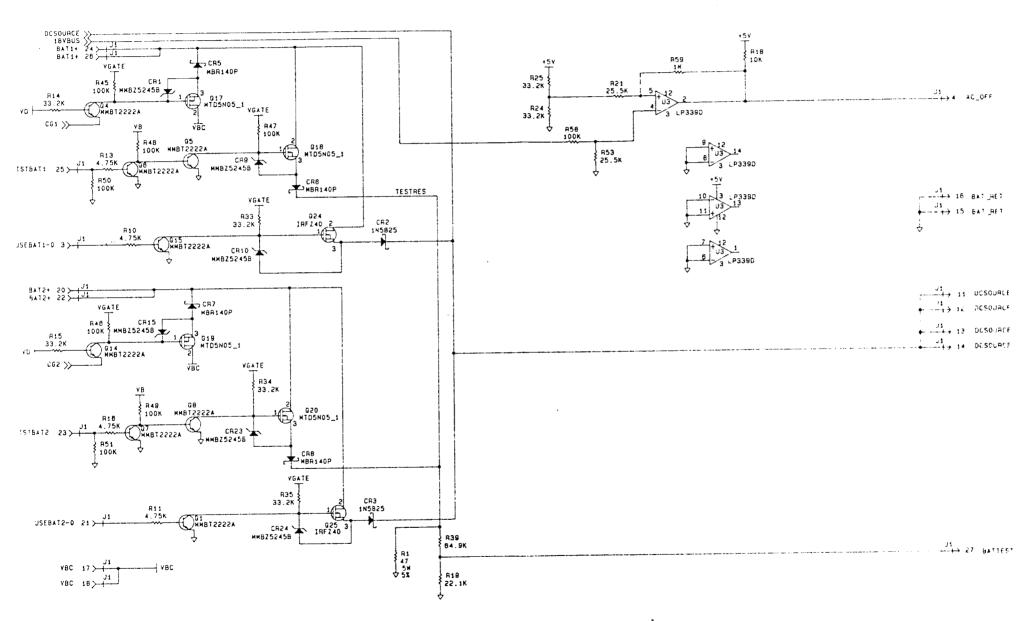

| SECTION 2. THEORY OF OPERATION Continued | 2.4.5<br>2.4.5.1<br>2.4.5.2<br>2.4.5.3<br>2.4.5.4<br>2.4.5.5<br>2.4.5.6<br>2.4.5.7<br>2.4.5.8<br>2.4.6.1<br>2.4.6.2<br>2.4.6.3<br>2.4.6.3<br>2.4.6.4<br>2.4.7 | Battery Switch Board Battery Switch Power Supply Battery to DC Source Switch Battery to Test Load Switch External Power Sources 18V Bus Detector Power Supply Control Latch Battery Charger Controller Connector Signal Description Power Supply Board Low Voltage Converter Line Power Converter Battery Charger Control Logic Motherboard | 2-48<br>2-49<br>2-50<br>2-51<br>2-51<br>2-52<br>2-52<br>2-54<br>2-55<br>2-56<br>2-57<br>2-60<br>2-61 |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

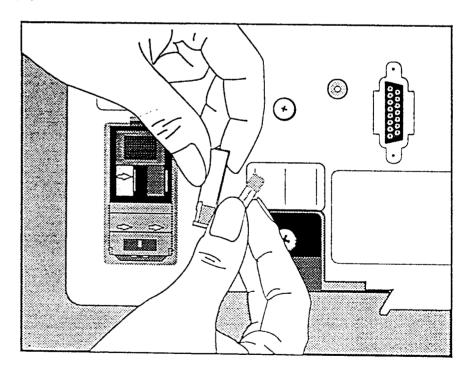

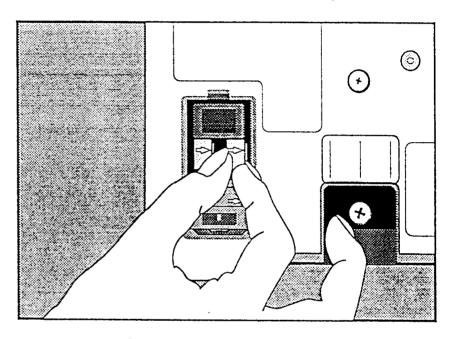

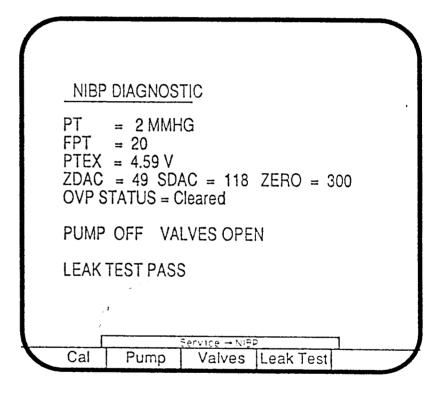

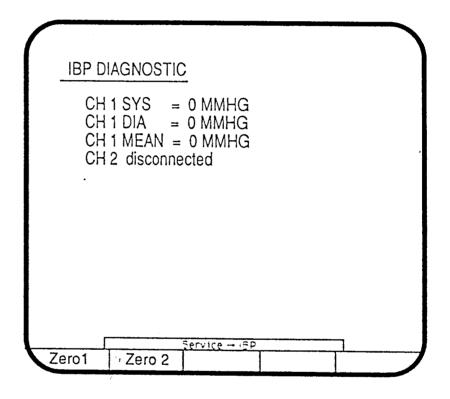

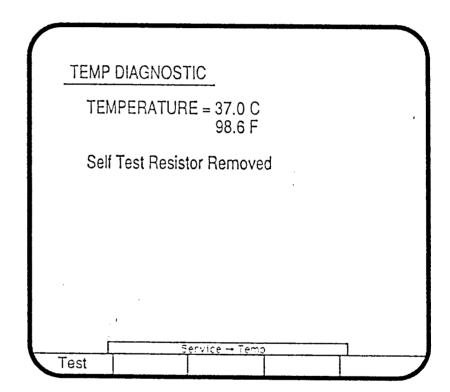

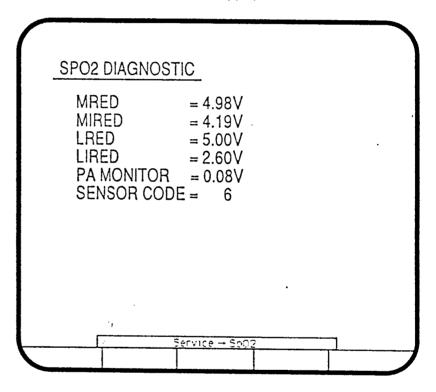

| SECTION 3. MAINTENANCE                   | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>3.4<br>3.4.1<br>3.4.1.1<br>3.4.1.2<br>3.4.1.3<br>3.4.1.4<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6                  | Introduction Changing Fuses Line Power Fuse Replacement Battery Fuse Replacement Replacement of Backup Battery Service Mode Operation NIBP Tests Automatic Leak Test Pump Overpressure Test Valves Test Calibration Check IBP Tests Temperature Tests SpO2 Test More Tests Service Mode Exit                                                | 3-1<br>3-1<br>3-3<br>3-4<br>3-4<br>3-6<br>3-7<br>3-8<br>3-10<br>3-11<br>3-13<br>3-14<br>3-15         |

CONTINUED

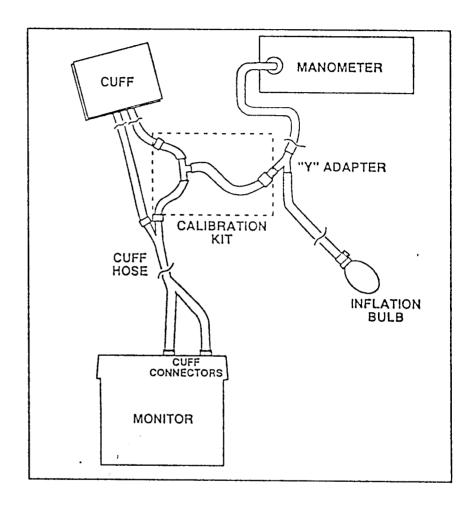

| SECTION 3. MAINTENANCE Continued                  | 3.5<br>3.5.1.1<br>3.5.1.2<br>3.5.1.3<br>3.5.1.4<br>3.5.2<br>3.6<br>3.7<br>3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.8.4<br>3.8.5<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14 | Periodic Maintenance As Required Integrity of Hoses and Cuffs Cleaning of Monitor Cleaning of Accessories Storage of Monitor Annual Procedures NIBP Leak Test NIBP Calibration Alignment and Adjustment Five Volt Logic Power Supply Battery Charger Float Voltage Twelve Volt Analog Power Supply Pneumatics System Pressure Switch Pulse Oximeter Tuned Transformers Jumper Options Alarm Code Interpretation Care of Storage Batteries Ground Resistance Test Disassembly Procedures Reassembly Procedures | 3-17<br>3-17<br>3-17<br>3-17<br>3-19<br>3-19<br>3-21<br>3-25<br>3-25<br>3-27<br>3-27<br>3-27<br>3-31<br>3-31<br>3-31 |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SECTION 4.<br>SERVICE DIAGRAMS<br>AND PARTS LISTS | 4.1<br>4.2                                                                                                                                                                | Introduction List of Applicable Service Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1                                                                                                           |

### LIST OF ILLUSTRATIONS

| 2-1   | Model 8720 System Block Diagram        | 2-2     |

|-------|----------------------------------------|---------|

| 2-2   | Pneumatics System Simplified Schematic | 2-8     |

| 2-3   | Power Distribution Diagram             | 2-12    |

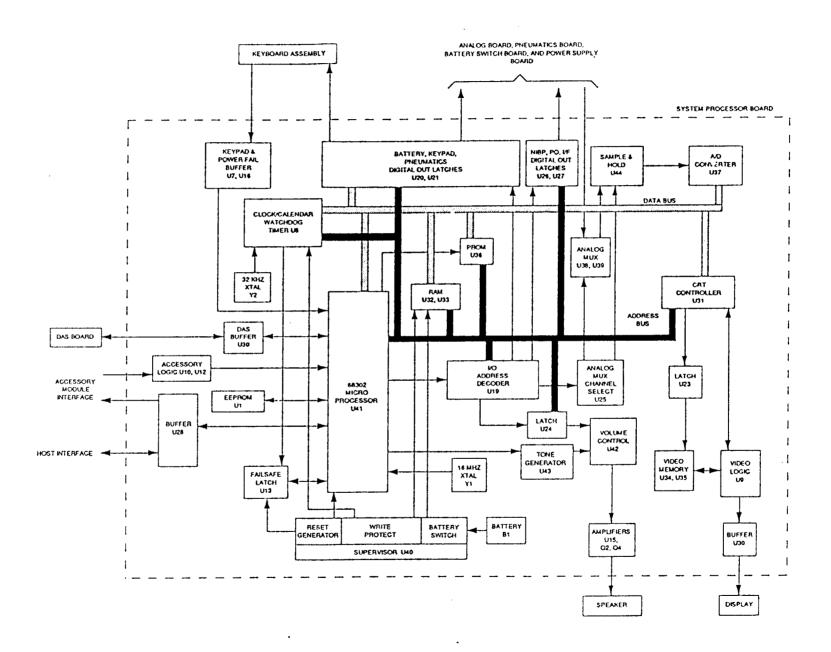

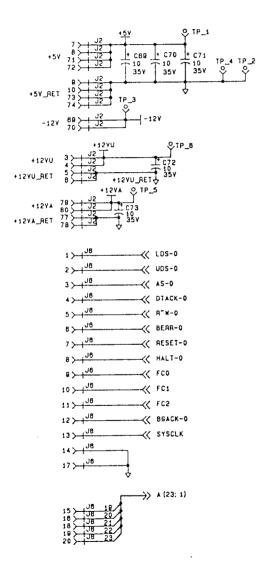

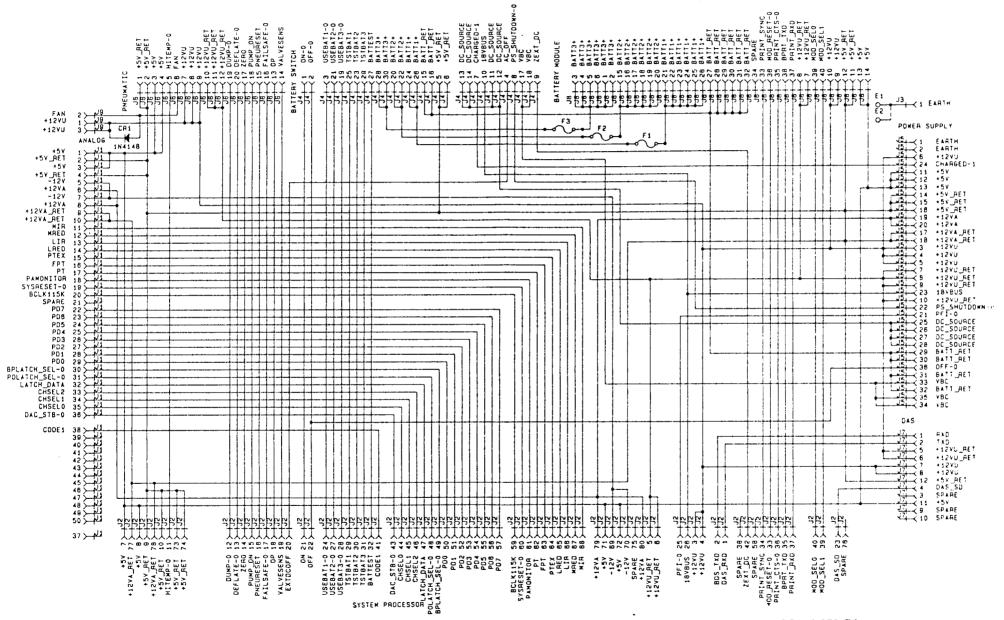

| FO-1  | System Processor Block Diagram         | 2-63/64 |

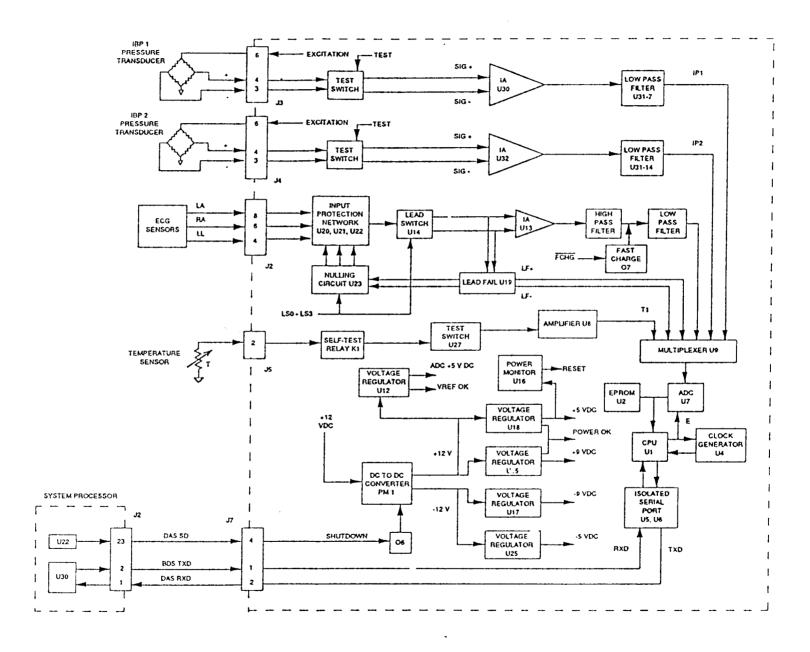

| FO-2  | Data Acquisition System Block Diagram  | 2-65/66 |

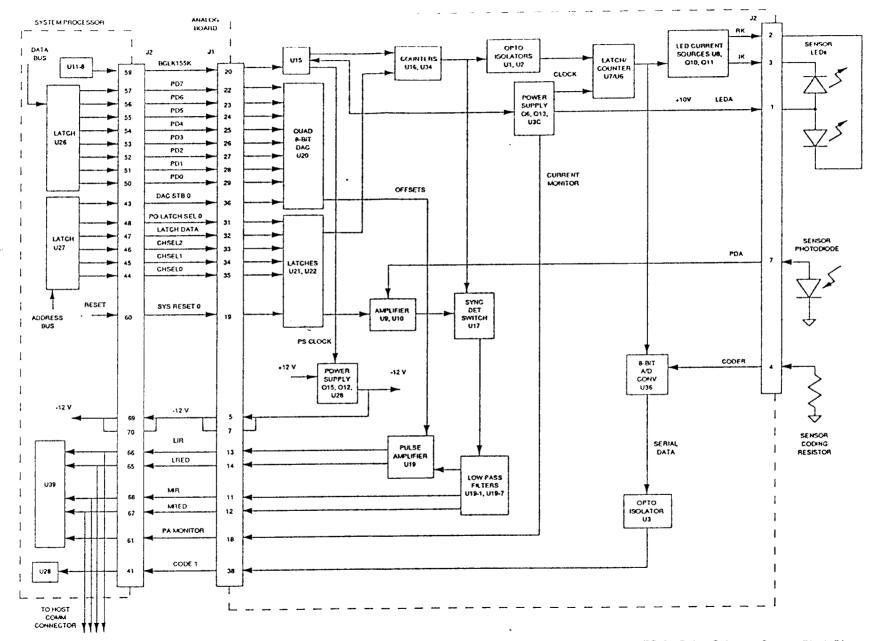

| FO-3  | Pulse Oximetry System Block Diagram    | 2-67/68 |

| FO-4  | Non-Invasive Blood Pressure System     |         |

|       | Block Diagram                          | 2-69/70 |

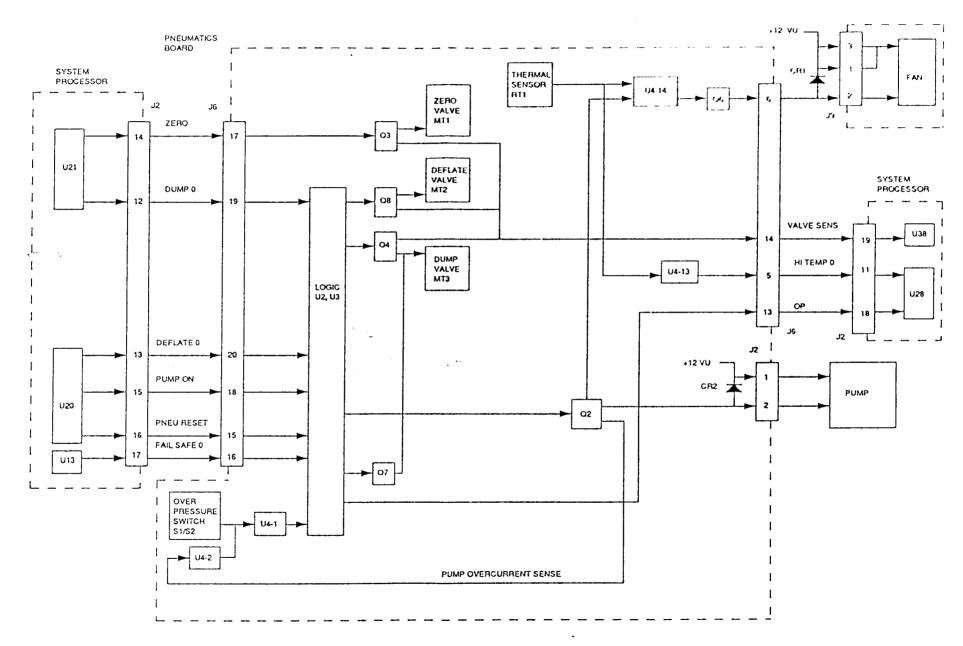

| FO-5  | Pneumatics System Block Diagram        | 2-71/72 |

| FO-6  | Power Supply Block Diagram             | 2-73/74 |

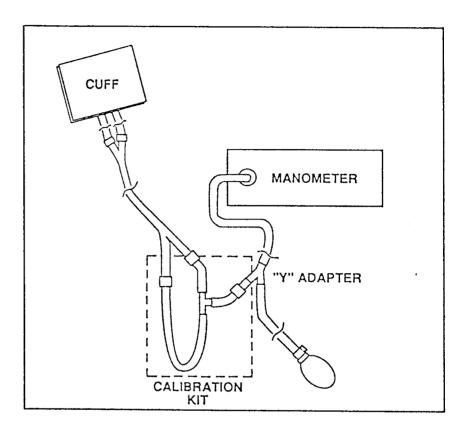

| 3-1 . | Pressure Calibration Check Setup       | . 3-11  |

| 3-2   | Cuif and Hose Leak Test Setup          | 3-20    |

| 3-3   | Model 8720 Interconnection Diagram     | 3-37    |

| 3-4   | Pneumatic Tubing Installation          | 3-39    |

| 4-1   | Top Assembly                           | 4-5/6   |

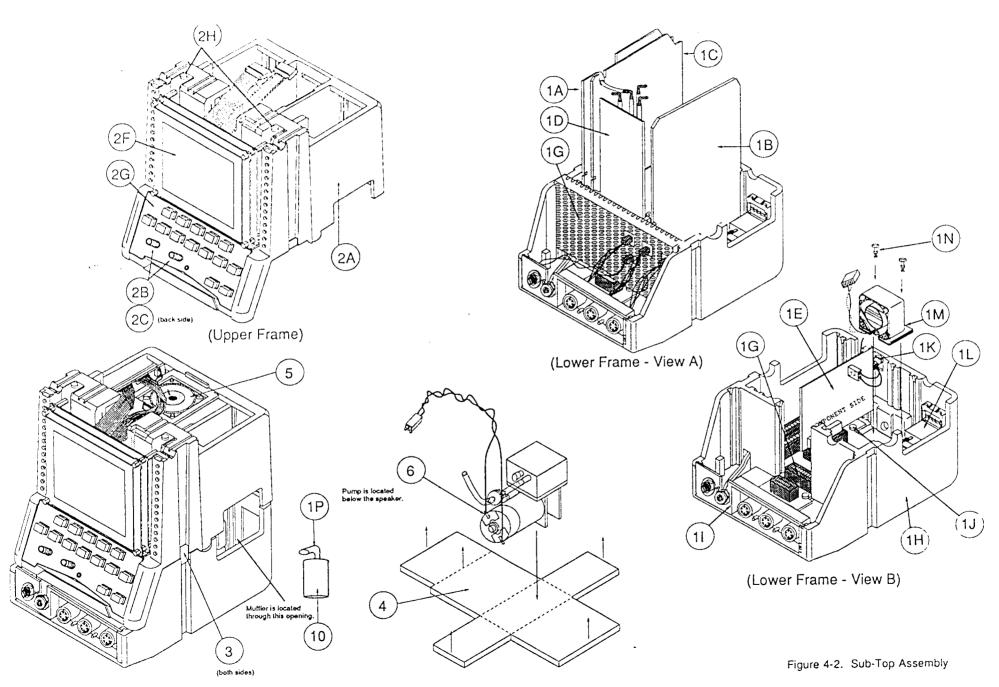

| 4-2   | Sub-Top Assembly                       | 4-7/8   |

### LIST OF TABLES

| 1-10         |

|--------------|

| 1-11         |

| 1-11         |

| 1-12         |

| 1-12         |

| 1-14         |

| 1-15         |

| 1-16         |

| cations 1-17 |

| 1-17         |

| 3-28         |

|              |

DINAMAP™ *PLUS* Vital Signs Monitor, Model 8720

#### SECTION 1. INTRODUCTION

#### 1.1 SCOPE OF MANUAL

This manual is intended for use by trained service technicians who are familiar with electromechanical devices and digital and analog circuit techniques. This Service Manual provides service and parts repair information for the DINAMAPTM PLUS Model 8720 Vital Signs Monitor.

#### WARNING

To reduce the risk of electric shock, do not remove cover or back. Refer servicing to qualified service personnel.

All unit repairs should be performed only by trained service technicians.

Voltages dangerous to life exist in this unit. Take care when servicing power supply and display assembly.

When troubleshooting power supply board, use an isolation transformer to isolate unit from ac line power. Use a variac and increase ac power input gradually while checking internal power circuit voltages.

For information about operating the Monitor in a clinical environment, refer to the separate Operation Manual.

The Service Manual consists of four sections:

Section 1 describes this volume and tells you how to use it. Information is provided about the physical and functional characteristics of the Monitor. Information is also provided about getting assistance in the event the unit fails to function properly.

- Section 2 presents theory of operation for the overall monitor, then provides descriptions of each of the main functions of the Monitor. Schematic diagrams of each major assembly are also described in detail as a further aid in understanding circuit functions.

- Section 3 provides information about periodic and corrective maintenance of the Monitor. Procedures are included for performance tests, calibration, pneumatic leak tests, cuff and hose leak tests, and alignment and adjustment. Corrective maintenance information is provided for isolating faults to the module/subassembly level.

- Section 4 contains Illustrated Parts Breakdown (IPB) drawings, service diagrams, and related parts lists.

#### 1.2 MANUAL CHANGES

If, in the normal use of this manual, you notice errors, omissions, or incorrect data, or if you can suggest comments that may help improve this manual, please complete the Publications Change Request form in the back of this manual. Submit the form to:

Critikon, Inc.

Marketing Services

P.O. Box 31800

4110 George Road

Tampa, Florida 33631-3800

Changes to the Service Manual, either in response to user input or to reflect continuing product improvements, are accomplished through reissue.

Changes occurring between reissues are addressed through Change Information Sheets and replacement pages. If a Change Information Sheet does not accompany your manual, the manual is correct as printed.

#### 1.3 SERVICE POLICY

All repairs on products under warranty must be performed by Critikon personnel. Unauthorized repairs will void the warranty. Products out of warranty should be repaired by Critikon or a Critikon authorized affiliate repair facility.

#### 1.3.1 Technical Assistance

If the product fails to function properly or requires maintenance and technical assistance is required, contact Critikon Technical Support.

Before contacting Technical Support:

- Have you checked the maintenance section of the Service Manual?

- Can you duplicate the problem? Please try to repeat the steps that initially caused the problem to appear.

- Make sure your accessories are not the cause of the problem. Many repairs can be avoided by checking all the accessories associated with the product.

If you are unable to resolve the problem after checking these items, please contact a Technical Support Specialist in one of the following ways:

#### 1.3.1.1 Via Phone

- Call Critikon Technical Support Monday through Friday, 8:30 AM to 5:00 PM, Eastern Time at 1-800-237-5591.

- Please tell the person answering your call that you need Technical Support.

- We are interesting in providing all our customers the assistance they need, and we will take the time to answer all of your questions. When calling, please be prepared to wait a short time while we offer assistance to callers ahead of you.

- Please have your service manual and a description of the problem available when you call.

#### 1.3.1.2 Via FAX

- We give priority to phone inquiries, so we might need some extra time (up to two days) to provide you a satisfactory reply via FAX.

- If you send a FAX, please include the following information:

Your complete name and address

Your phone number

Your FAX number

The model and serial number of the product

A complete description of the problem or request

- We may choose to call you by phone even when you send a FAX

- The FAX number for Critikon Technical Support is 1-813-286-7119

#### 1.3.2 Repair Service

To obtain repair service, phone Critikon Repair Service Monday through Friday, 8:30 AM to 5:00 PM Eastern Time at 1-800-237-5591.

Please tell the person answering your call that you need Repair Service.

State your:

Hospital Name

Address

Telephone Number

Model and Serial Number

Complete Description of the Problem

- Critikon's Product Service Representative will advise you of the corrective action required. If you are advised to return the product to Critikon for repair, do the following:

- 1. Package the product with adequate protection. If available, use the original materials shipped with the product.

- 2. Include a brief description of the problem, as well as the name, address, and phone number of the person to be contacted for additional information.

- 3. Include the Return Authorization Number (RA#) and a purchase order number.

- 4. Ship the product, transportation prepaid, to the Product Service Center specified by your Product Service Representative. Repairs will be made at the service facility and the product will be returned to the purchaser prepaid.

#### 1.3.3 Repair Parts

To obtain information on or to order repair parts, phone 1-800 237-5591 Monday through Friday, 8:30 AM to 5:00 PM Eastern Time.

Please tell the person answering the phone that you need Repair Parts.

#### 1.4 PRODUCT DESCRIPTION

#### 1.4.1 General Description

The 8700 series DINAMAPTM PLUS Vital Signs Monitors are portable devices used for noninvasive and invasive monitoring of patients in numerous clinical settings. Each Monitor can accompany patients to and from various hospital departments (emergency, radiology, recovery, cardiac step-down) and can be used during many specialized procedures in satellite areas, or during surgeries in physicians' offices or ambulatory surgery centers.

The Monitor can be battery powered when connected to an optional battery module, Critikon Reorder No. 8725. The Monitor can also run on AC power using a standard power cord.

The battery module uses two user-replaceable batteries. Battery usage is sequential; as the life of one battery diminishes, operation automatically switches to the other. The drained battery can be replaced with a fully charged spare for continuous and indefinite battery operation.

The Monitor is available in three models: Model 8700 features measurement of noninvasive blood pressure (NIBP) and blood oximetry (SpO2); Model 8710 adds ECG measurement to the features of the Model 8700; Model 8720 includes patient temperature measurements and has two invasive blood pressure measurement channels in addition to the features of the Model 8710.

#### 1.4.2 Physical Description

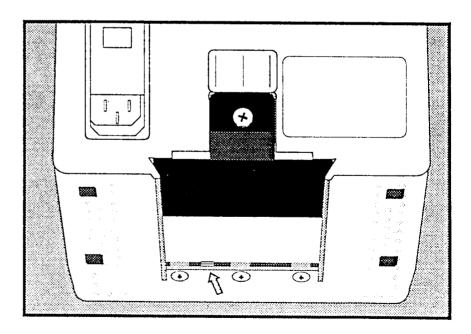

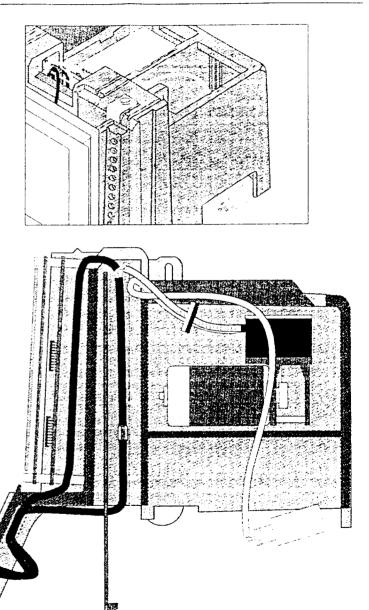

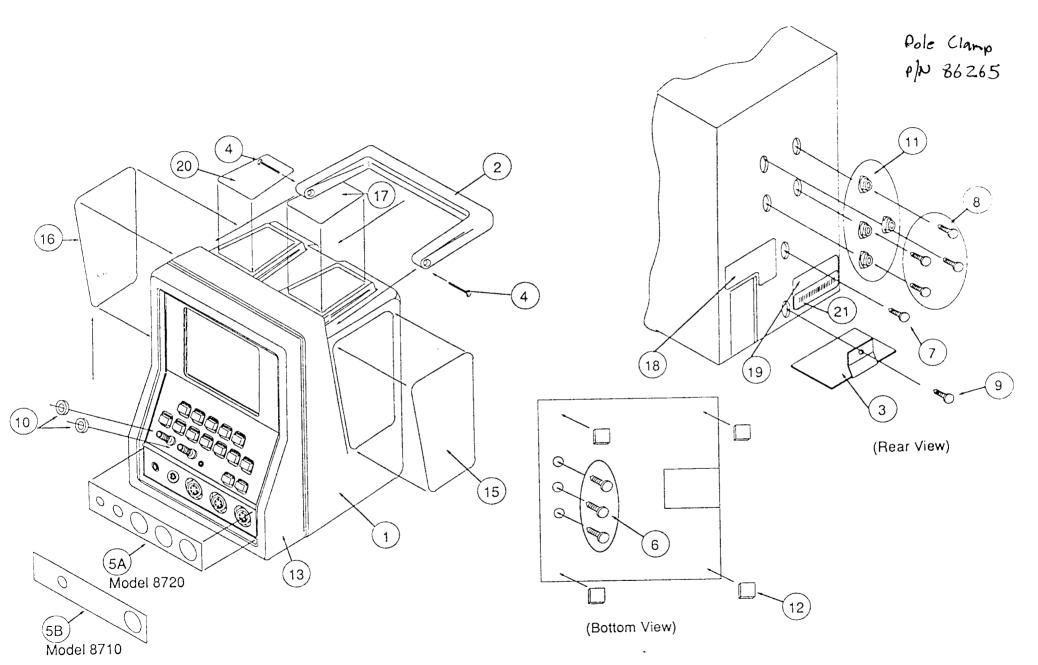

The Monitor consists of the accessory kits and the monitor unit itself. The Monitor unit top assembly is comprised of the bezel, case, handle, mounting plate, and mounting hardware. When the top assembly is removed, the upper and lower frame assemblies are exposed.

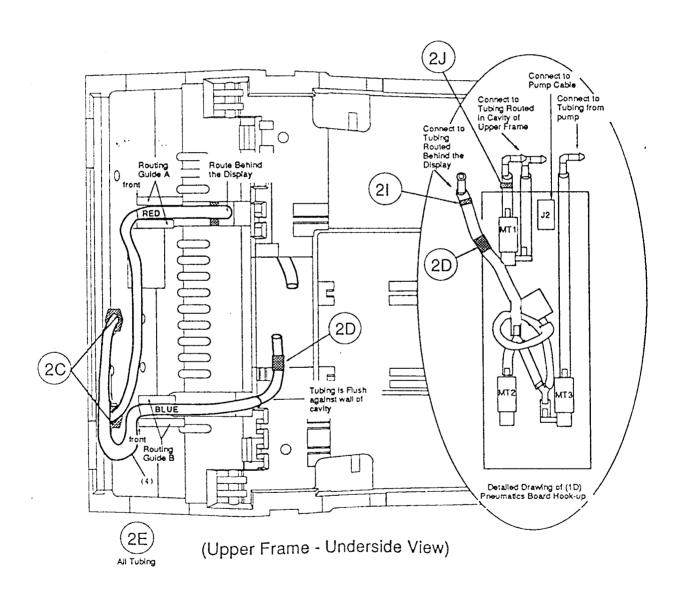

The upper frame assembly includes the upper frame; keyboard assembly and cable; and display, mounting bracket, and cable. The pump assembly, pneumatic hoses and pump cable, speaker assembly and cable, muffler, and pump foam mount are also attached.

The lower frame assembly comprises the lower frame, connector assembly, fan assembly, power entry assembly and cables, and external dc connector and cable. The assembly also houses eight printed wiring boards, including the system processor board, pneumatics board, analog board, power supply board, battery switch board, DAS board (models 8710 and 8720), and motherboard.

### 1.4.3 Storage Batteries

The storage battery specified for use with the DINAMAP™ *PLUS* Monitor is a sealed lead-acid battery. It was selected for its high capacity (2.3 Amperes per hour for standard 10 hour rate), quick-charge ability (recharge time as little as two hours) and ease of replacement (has pressure contacts).

The expected battery cycle life is largely dependent on the way the battery is used. If the battery is allowed to be fully discharged after each use and then fully recharged soon after use, the battery should last for the full two hundred recharge life cycle. If a battery is used in the top one third of its charge and fully charged whenever possible, up to twelve hundred cycles can be expected, approximately six times the number of cycles used to 100% capacity.

A battery that has been fully discharged can be fully charged by the Monitor in less than five hours. If any storage batteries are in the battery module while the Monitor is connected to an external AC power source (even if the Monitor is off) the monitor will attempt to charge the batteries. If more than one battery is to be charged, the Monitor will automatically charge the second battery after the first battery either becomes fully charged or is removed from the battery module.

A fully charged battery can be stored up to six months and retain as much as 80% of its capacity. One fully charged battery will supply enough energy to operate the Monitor for approximately one hour. This operation would include continuous ECG, invasive blood pressure, temperature, pulse oximetery and non-invasive blood pressure operations set at five minute determinations.

| Run Time | Typical Charge Time  |

|----------|----------------------|

| 10 min   | 45 min (0.75 hours)  |

| 20 min   | 90 min (1.5 hours)   |

| 30 min   | 135 min (2.25 hours) |

| 40 min   | 180 min (3.0 hours)  |

| 50 min   | 225 min (3.75 hours) |

| 60 min   | 270 min (4.5 hours)  |

#### 1.4.4 Product Reorder Information

#### Model 8700 - NIBP and pulse oximetry

Includes monitor, power cable, adult DURA-CUFTM blood pressure cuff, 12-foot air hose, NIBP calibration kit, SpO2 sensor, SpO2 system cable, and operation manual.

Model 8710 - NIBP, pulse oximetry, and ECG

Includes monitor, power cable, adult DURA-CUFM blood pressure cuff, 12-foot air hose, NIBP calibration kit, SpO2 sensor, SpO2 system cable, ECG cable, 3 ECG electrodes, 3 ECG lead wires, and operation manual.

Model 8720 - NIBP, pulse oximetry, ECG, temperature, and 2-channel invasive pressure

Includes monitor, power cable, adult DURA-CUFM blood pressure cuff, 12-foot air hose, NIBP calibration kit, SpO2 sensor, SpO2 system cable, ECG cable, 3 ECG electrodes, 3 ECG lead wires, YSI temperature cable, and operation manual.

#### 1.4.5 Accessory Reorder Information

#### 1.4.5.1 Critikon Accessories

Accessories available from Critikon are listed in Table 1-1.

#### 1.4.5.2 After-Market Accessories

The Monitor may also be used with certain equipment supplied by other manufacturers. For further information about the compatibility of such equipment, contact the Johnson & Johnson sales representative. The items listed below are known to have compatibility problems with the Monitor, and should not be used.

Transducers - The Monitor is not designed to work with 40μV/V/mmHg transducers such as Hewlett-Packard Models 267, 268, 1280, and 1290A.

Transducer cables - Viggo Spectramed cables with built-in preamplifiers that boost the signal of a  $5\mu V/V/mmHg$  transducer to  $40\mu V/V/mmHg$  and terminate in the H-P 12-pin connector will not work with the Monitor, even when connected by the Fogg Systems cable.

Intracranial pressure - The Monitor is not compatible with the Camino Intracranial Pressure transducers

The Monitor is also not designed to work with the following cables:

TC-HPO-2 TC-HPO-8040 TC-HPO-8030H TC-HPO-8040H

#### 1.4.6 Specifications

Monitor mechanical specifications are listed in Table 1-2, environmental specifications are listed in Table 1-3, and electrical specifications are listed in Table 1-4. Performance specifications are listed in Tables 1-5 through 1-10.

Table 1-1. Critikon Accessories

| Accessory | Description                                                                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8725      | Battery module, including 2 rechargeable lead/acid storage batteries                                                                                                                               |

| 8726      | Waveform printer module, including 2 rechargeable lead/acid storage batteries                                                                                                                      |

| 8727      | External battery charger, holds up to 4 batteries for fast recharge                                                                                                                                |

| 8728      | Heavy duty, woven nylon carrying case, with zippered main<br>monitor compartment, three pockets with hook and loop<br>closures for accessory items, carrying handle, and padded<br>shoulder strap. |

| 8729      | Text printer module, including 2 rechargeable lead/acid storage batteries                                                                                                                          |

| 8730      | Thermal printer paper, 10 rolls per box.                                                                                                                                                           |

| 8731      | SpO2 system cable, for use with 9084 SpO2 sensor                                                                                                                                                   |

| 8732      | Domestic ECG cable kit, includes 3 (AHA red, black, and white) disposable electrodes, 3 lead wires, cable, instruction sheet                                                                       |

| 8733      | Pole mount                                                                                                                                                                                         |

| 8742      | International ECG cable kit, includes 3 (AHA yellow, green, and black) disposable electrodes, 3 lead wires, cable, instruction sheet                                                               |

| 9084      | SensorMedics OMNI-SAT™ SpO2 sensor, for use with 8731 system cable                                                                                                                                 |

Table 1-2. Mechanical Specifications

<u>ITEM</u> <u>DESCRIPTION</u>

MONITOR WEIGHT 9.8 lbs (4.45 kg)

BATTERY MODULE 3.85 lbs (1.75 kg)

WEIGHT

DIMENSIONS 9.25 inches high; 7.2 inches wide; 8.5 inches

deep 235 x 18.3 x 216 cm

BATTERY MODULE 1.5 inches high; 7.2 inches wide; 8.0 inches deep

DIMENSIONS 3.8 × 19.3 x 20.4 cm

ELECTROLUMINESCENT 320 by 256 pixels

DISPLAY Viewing area 3.8 inches wide by 3.0 inches high

MOUNTINGS Surface mount or optional pole mount

#### Table 1-3. Environmental Specifications

### ITEM <u>DESCRIPTION</u>

OPERATING TEMPERATURE 50° F to 104° F (10° C to 40° C)

OPERATING ALTITUDE -1000 to 15,000 ft (-305 to 4570 m)

STORAGE TEMPERATURE 29° F to 167° F (-34° C to 75° C)

RELATIVE HUMIDITY 0 to 90 percent, noncondensing

LEAKAGE CURRENT Less than 100 μA

Table 1-4. Electrical Specifications

| ITEM                      | DESCRIPTION                                                                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC INPUT VOLTAGE          | 88 to 268 VAC, 47 to 63 Hz                                                                                                                            |

| AC INPUT POWER            | 20-35 watts typical, including battery charger 70 watts maximum                                                                                       |

| AC LINE FUSES             | 2.0 A                                                                                                                                                 |

| DC INPUT VOLTAGE          | 8 to 32 VDC                                                                                                                                           |

| DC INPUT POWER            | 15-21 watts typical; 42 watts maximum                                                                                                                 |

| BATTERY PÄCK<br>OPERATION | Two batteries; sequential operation, one hour per battery, except 15 minutes per battery in NIBP mode Standard 10 hour rating is 2.3 Amperes per hour |

| POWER CABLE               | Detachable, blue jacketed, 16 gauge, 10 foot length In USA, terminated in medical grade 3-prong plug International cable unterminated                 |

Table 1-5. NIBP Performance Specifications

| ITEM                      | ADULT DESCRIPTION | NEONATE DESCRIPTION |

|---------------------------|-------------------|---------------------|

| CUFF PRESSURE<br>RANGE    | 0 to 250 mmHg     | 0 to 220 mmHg       |

| INITIAL CUFF<br>INFLATION | 178 ± 15 mmHg     | 125 ± 15 mmHg       |

| MAP<br>DETERMINATION      | 20 to 225 mmHg    | 20 to 170 mmHg      |

| SYSTOLIC<br>DETERMINATION | 30 to 245 mmHg    | 30 to 190 mmHg      |

Table 1-5. NIBP Performance Specifications (Continued)

| ITEM                            | ADULT DESCRIPTION                                                                                                        | NEONATE DESCRIPTION    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|

| DIASTOLIC<br>DETERMINATION      | 10 to 210 mmHg                                                                                                           | 10 to 160 mmHg         |

| DETERMINATION<br>TIME           | Manual/Auto Mode 20 to 45 sec typical; 120 sec maximum STAT Mode 19 sec typical at nominal blood pressure and heart rate | Same                   |

| OVERPRESSURE<br>CUTOFF          | 300 mmHg +30, -48 mmHg                                                                                                   | Neonate 235 ± 10 mmHg  |

| PULSE RATE<br>RANGE             | 40 to 200 mmHg                                                                                                           | Neonate 40 to 220 mmHg |

| PULSE RATE<br>ACCURACY          | Within one standard deviation (68 % of all readings), or ± 3.5 %                                                         | Same                   |

| PRESSURE<br>DISPLAY<br>ACCURACY | ± 3 mm Hg                                                                                                                | Same                   |

| HEART RATE<br>RANGE             | 40 to 200 bpm                                                                                                            | Same                   |

| SYSTOLIC ALARM<br>LIMITS        | High 75 to 245 mmHg<br>Low 30 to 150 mmHg                                                                                | Same                   |

| DIASTOLIC ALARM<br>LIMITS       | High 50 to 210 mmHg<br>Low 10 to 120 mmHg                                                                                | Same                   |

#### Table 1-6. ECG Performance Specifications

<u>ITEM</u> <u>DESCRIPTION</u>

OVERLOAD PROTECTION AC Voltage 1V p-p @ 60 Hz for 10 sec on all

leads

Defibrillator Protection Maximum 8 sec recovery

from 5 kV

Patient Connection Risk Current Less than 10µA

Single Fault Risk Current Less than 50 µA

QRS DETECTION Tall T Wave Rejection 100 %

Range of Amplitude 0.5 to 5.0 µV; no response

when less than  $0.15 \,\mu\text{V}$

Range of Duration 70 to 120 msec; no response

when less than 10 msec 60 Hz Voltage

Tolerance (QRS=0.5 mV, 100 msec) 250 µV p-p Drift Tolerance Detect a QRS of 0.5 mV; 100 msec; 80 bpm w/o,1Hz; 4 mV triangle wave

HEART RATE METER Range 10 to 250 bpm

Accuracy  $\pm$  3 bpm, or  $\pm$  3 % of reading

High Heart Rate Response Time Less than 5

seconds

Low Heart Rate Response Time Less than 10

seconds

ALARMS High Range Limit 80 to 250 bpm

Low Range Limit 10 to 140 bpm Resolution of Settings 5 bpm

TIME TO ALARM Tachycardia Less than 5 seconds

Cardiac Standstill, 0 to 60 bpm Less than 5

seconds

Low Heart Rate, 40 to 80 bpm Less than 10

seconds

High Heart Rate, 80 to 120 bpm Less than 10

seconds

SPECIAL REQUIREMENTS Input Dynamic Range ± 5 mV

Input Impedance Greater than 2.5 Megohm

System Noise Less than 20 µV p-p

Multichannel Crosstalk Less than 1 % of input

#### Table 1-6. ECG Performance Specifications (Continued)

ITEM <u>DESCRIPTION</u>

GAIN CONTROL Gain Selection 40, 30, 30, 10, 5 mm per m

Gain Switching Manual or Auto

TIMEBASE Selection 50, 25, 12.5 mm per second

Accuracy Within ± 10 %

OUTPUT DISPLAY Minimum Channel Width 30 mm

Aspect Ratio 0.4 ± 0.08 seconds per mV

ACCURACY OF SIGNAL Maximum System Error  $\pm$  20 %, or  $\pm$  100  $\mu$ V

Frequency Response 0.5 to 40 Hz Maximum Hysteresis 0.5 mm

Standardizing Voltage 1 µV

Common Mode Rejection Less than 5 %

#### Table 1-7. SpO2 Performance Specifications

ITEM <u>DESCRIPTION</u>

ACCURACY  $\pm$  1% at standard deviation;  $\pm$  2% at 90 to 99%;

± 3% at 75 to 89%; unspecified at less than 75%

SATURATION RANGE 40 to 99 %

PULSE RATE 30 to 250 bpm

PULSE AVERAGING User selectable from 0 to 30 seconds in

increments of 3 seconds; at power up, preset at 6

seconds

SATURATION PITCH

INDICATOR

Pitch changes with saturation; tone volume selectable from maximum to completely silent.

SATURATION ALARM

LIMITS

High 90 to 99%; low 40 to 95%

#### Table 1-8. IBP Performance Specifications

**ITEM DESCRIPTION**

NUMBER OF CHANNELS Two

**RANGE** -30 to 300 mmHg

DISPLAY SCALES Selectable in 10mmHg increments

TRANSDUCER SENSITIVITY 5μV/V/mmHg

**GAIN ACCURACY** ± 1% or ± 2 mmHg of reading, whichever

is greater

GAIN DRIFT" ± 0.42 mmHg per °C

ZERO ADJUSTMENT ±150 mmHg

ZERO ACCURACY ±1 mmHq

ZERO DRIFT ± 0.23 mmHg per °C

BANDWIDTH DC to 40 Hz

PULSE RATE RANGE 10 to 250 bpm

SYSTOLIC ALARM LIMITS High 20 to 300 mmHg

Low 30 to 150 mmHg

DIASTOLIC ALARM LIMITS High 20 to 300 mmHg

Low 30 to 120 mmHg

MEAN ARTERIAL PRESSURE

High 20 to 300 mmHq **ALARM LIMITS** Low 30 to 120 mmHg

Table 1-9. Temperature Performance Specifications

**ITEM**

DESCRIPTION

CONNECTOR

YSI 400 compatible

**BANGE**

89.6° F to 107.6° F (32° C to 42° C)

SCALE SELECTION

°F or °C

ACCURACY

± 0.1° C, not including tolerance of probe

RESOLUTION

0.1° C or 0.1° F

SELF TEST

$37.1 \pm 0.1$  °C (98.8 ± 0.4 °F) internal, manual

ALARM LIMITS

High 89.6° F to 107.6° F (32.0° C to 42.0° C) Low 89.6° F to 107.6° F (32.0° C to 42.0° C)

Table 1-10. Alarm Functions

ITEM

DESCRIPTION

SYSTEM ALARM

INTERNAL TEST

Performed at power up and during operation

NIBP PROCEDURAL

**ALARMS**

Overpressure

Excess determination time Excess pump-up time

Lack of determination

OXYGEN SATURATION

Low signal

PROCEDURAL ALARMS

Probe disconnection

Probe failure

**VOLUME LEVEL**

Selectable from minimum to maximum on all

parameters

### SECTION 2. THEORY OF OPERATION

### 2.1 INTRODUCTION

This section contains theory of operation for the Monitor. Overall operation is described in paragraph 2.2. Refer to paragraph 2.3 for a description of each functional system. Detailed theory for each circuit board is provided in paragraph 2.4.

#### 2.2 SYSTEM THEORY OF OPERATION

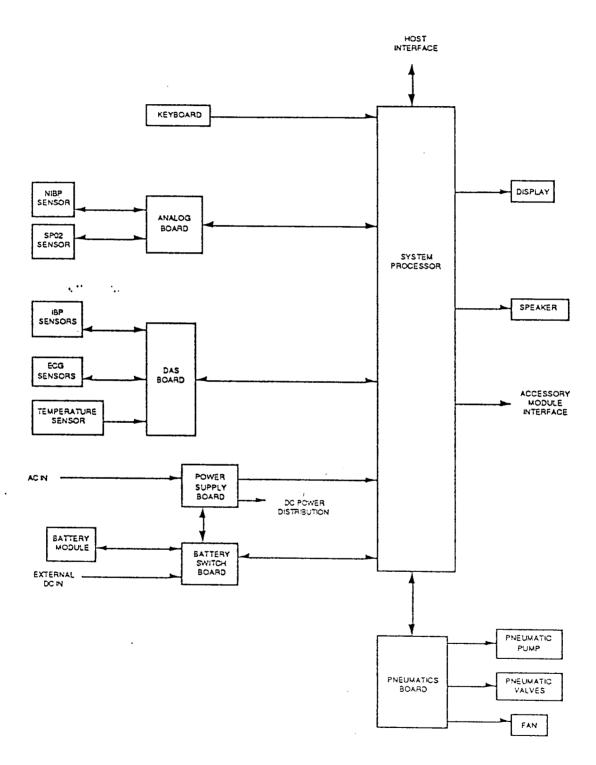

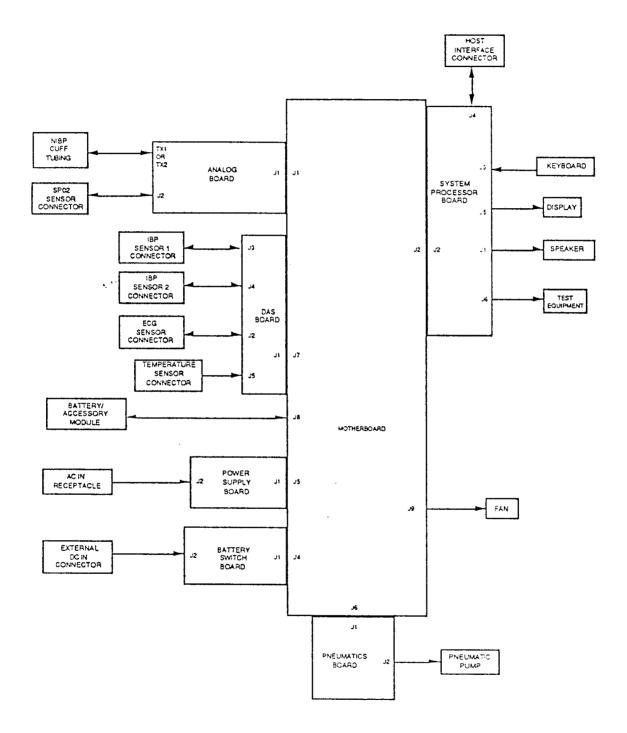

A system block diagram of the model 8720 Monitor is shown in Figure 2-1. The patient vital signs are measured by a variety of electronic sensors. The non-invasive blood pressure and pulse oximetry measurements are controlled by the analog board. The Data Acquisition System (DAS) board provides a similar function for the invasive blood pressure, ECG, and temperature measurements. The sensor measurement operations of each board are supervised by the system processor, which converts the results into visual and aural presentations at the electro-luminescent display and audio loudspeaker.

Operator access is via a keyboard, and an interface accessory is available to provide a hard copy printout from an optional printer. Data interchange between the system processor program and a host computer is provided by a communications interface.

The Monitor includes a pneumatics system required for NIBP operation. The pneumatics board regulates the operation of the pneumatic pump, valves, and cooling fan. The Monitor can be operated from ac power, storage batteries, or an external dc power source. The power supply board rectifies the ac power, recharges the batteries, and provides regulated dc operating power for the Monitor. The battery switch board provides power supply monitoring and control under supervision of the system processor.

Figure 2-1. Model 8720 System Block Diagram

Models 8700 and 8710 Monitors differ from the above description in that the invasive blood pressure and temperature channels are not available, and the ECG channel is also not available on the Model 8700.

#### 2.3 FUNCTIONAL THEORY OF OPERATION

The following paragraphs provide a simplified description of each of the Monitor functional systems. Foldout (FO) diagrams are located at the end of this section. Information about input and output sources and destinations, along with connector pin identifications, is included as an aid to troubleshooting. Refer to paragraph 2.4 for complete circuit details.

#### 2.3.1 System Processor

The system processor (Diagram FO-1) is based on Motorola 68302 microprocessor (CPU) U41. The microprocessor incorporates failsafe logic that causes the Monitor to enter a safe state if microprocessor operation ceases.

RAM consists of 256K bytes of battery backed read-write memory. To maintain RAM contents, the memory logic supply, controlled by supervisor U40, automatically switches to the battery supply in the event of power failure. The program storage ROM consists of single socket U36 for 16-bit word EPROM or PROM devices. EEPROM U1 contains the NIBP pressure calibration constants and unit model number used to configure the Monitor for the appropriate parameter set and language option. A real time battery-backed clock is provided that allows the user to set time and date for time stamping for trend displays and for waveform and tabular printouts.

The system processor communicates with the DAS board via 62.5K bit/sec serial bidirectional CMOS interface U30. Additional interfaces provide digital inputs and outputs with the analog board, pneumatics board, battery switch board, and power supply.

The CPU is provided with a serial communications interface to an external host. Receive data, transmit data, and clock signals are routed via host buffer U28. Baud rates are software programmable from 300 to 76.8K bits/sec. The system processor also has a bidirectional serial interface to an optional graphics array printer or other serial device. The bit rate is programmable from 300 to 76.8 bits/sec.

The electroluminescent display is managed by Hitachi HD63484 advanced CRT controller (ACRTC) U31. The display image is a composite of overlaid foreground and background screens. The graphics subsystem has 128K x 16 bit RAM U34, U35 to store graphics images. Graphics images for alphanumeric and special characters are handled directly by the software.

The microprocessor includes audio tone generator U43, used for alarms, QRS detect tones, audio key feedback, and proportional pulse tones related to SpO2 saturation level. Frequencies and volume levels of the audio tones are software selectable at U42.

## 2.3.2 Data Acquisition System

The data acquisition system (FO-2) for Model 8720 incorporates subsystems for invasive blood pressure, ECG, and temperature signal processing. Model 8710 uses only the ECG subsystem. Overall operation of the DAS is controlled by DAS CPU U1. Patient vital sign measurements and DAS status and error conditions are relayed to the Monitor system processor via J7-2 from isolated serial port U5. The system processor sends initialization, calibration, configuration, and test commands to isolated port U6 via J7-1. The channel inputs to multiplexer U9 are routed to U7 for conversion to the digital format required for CPU processing.

The patient temperature is sensed by the value of the transducer resistance applied to test switch U27 via relay K1. The relay allows the system to compare this input with that of a precision resistor for self testing. The test switch is used to help determine what gain errors exist in amplifier U8. The amplified signal is applied to one of the inputs of multiplexer U9.

The patient blood pressure is sensed by the resistive bridge transducer connected to either of the two invasive pressure channel inputs. Transducer excitation is buffered from the +5 volt supply. Each transducer input is applied to a test switch that allows a self test signal to ensure channel gain and offset accuracy. The instrumentation amplifier (IA) output is then filtered and passed to multiplexer U9.

Patient ECG is measured by a three lead sensor connected to an input protection network. The network protects the input from interference from electrosurgical noise and defibrillator voltages. A lead switch circuit allows the DAS CPU to switch the input among the three standard ECG sensor leads, as selected by the user from the front panel. The lead fail circuit and common nulling loop provide lead compensation that ensures the accuracy of the ECG measurements. The instrumentation amplifier output is filtered by a network that employs a fast charge control circuit that maintains the filter time constant.

The DAS power supply provides for patient isolation from earth ground. The supply consists of medical grade dc to dc converter PM1 and four linear voltage regulators. A shutdown command from the Monitor system processor is applied to PM1 from J7-1 via Q6 to save power when the DAS functions are not being used.

The output from +5 volt supply regulator U18 is monitored by U16, and any undervoltage swings result in a DAS reset command from U16. A POWER OK signal from the regulator is also monitored by the DAS CPU for voltage errors or if current or thermal limits are exceeded at U18. The POWER OK signal from +9 volt supply regulator U15 operates similarly. The -9 volt output from regulator U17 is monitored for errors by the multiplexer. Any faults that may occur in the -5 volt supply provided by regulator U25 are detected by errors at the ADC.

#### 2.3.3 Pulse Oximetry System

The pulse oximetry system (FO-3) provides continuous readings of oxygen saturation and pulse rate. The physiological signals produced by a photodiode in the oximeter sensor are applied to the analog board at J2-7 and amplified by U9 and U10. The signals are then fed to synchronous demodulator U17. After filtering by amplifier U19, the demodulated saturation signals MIR and MRED are routed to the Monitor system processor for A/D conversion. The sensor pulse component of the sensor signals is amplified by U19 and routed as LIR and LRED to the system processor. An adjustable offset voltage to U19 is set by DAC U20. The DAC output is controlled by digital data inputs PD0 through PD7 enabled by DAC STB 0 at J1-36. The master clock for the pulse oximetry subsystem is routed from the system processor to the analog board via J1-20.

The analog board also provides software-controlled adjustment of the AC drive current to the LEDs in the oximeter sensor. Power is supplied to the sensor interface by a push-pull switching power supply. U15 controls the current limit and on/off functions of the isolated power supply. The +10 volt power supply Q6, Q13 is derived from the master clock signal. Presettable binary counter U16 provides the carrier frequency reference clock for synchronous detector U17. The current flow from Q6, Q13 is monitored by the system processor via the PA monitor output from J1-18. The -12 volt power supply Q12, Q15 is also derived from the master clock. The system processor is provided -12 volt operating power via J1-5, 7.

Each sensor type (adult/pediatric or neonatal) contains a unique resistor connected at J2-4. The resistor value is read by A/D converter U36 and converted to bit serial data that is applied to opto-isolator U3. The data is then applied via J1-38 to the system processor to enable the appropriate selection of monitoring mode.

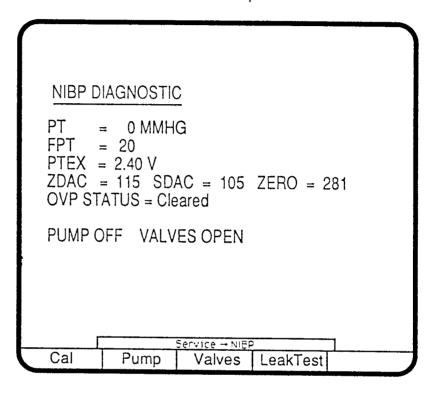

#### 2.3.4 NIBP System

The noninvasive blood pressure system (FO-4) uses the oscillometric technique to measure blood pressure and pulse rate. The signals from the pressure sensor are applied to preamplifier U23 within the analog board. Any of four types of pressure sensors can be used, as configured by jumpers and resistors. An unfiltered transducer output signal PT is routed to the system processor via J1-17. The signal is amplified and filtered to extract the pulse component. Low pass filtering is provided by U24-14, and the signal is then applied to high pass filter U24-8 and clamp U26. The filtered signal is routed to the system processor via J1-16. Addressable latch U22 is used to switch circuit gain between the adult/pediatric and neonatal monitoring modes.

The magnitude of the transducer amplifier offset from scaler/buffer U24-7 is software-adjustable by DAC U20 for auto-zero. Transducer excitation current or voltage for the pressure sensor is software adjustable for scale calibration. The magnitude of the excitation produced by current driver Q1, Q2 is set by DAC U20. The DAC scale and offset outputs are controlled by digital data inputs PD0 through PD7 enabled by DAC STB 0 at J1-36.

The system software includes an internal online self-test feature for the FPT channel at power-up and after each non-stat mode determination. Additionally, buffer U25-7 provides a measurement of the transducer excitation to the system processor for calibration verification.

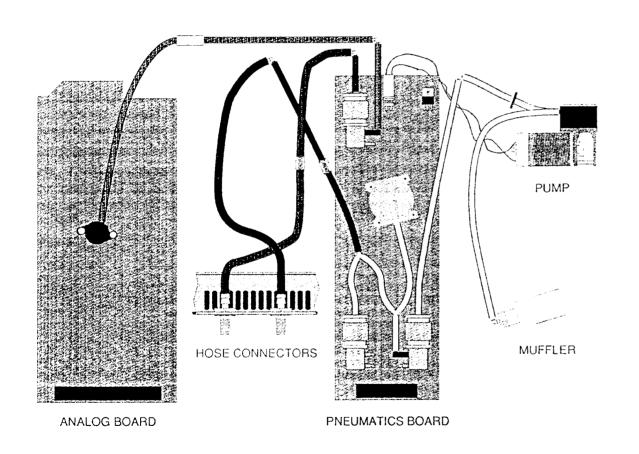

### 2.3.5 Pneumatics System

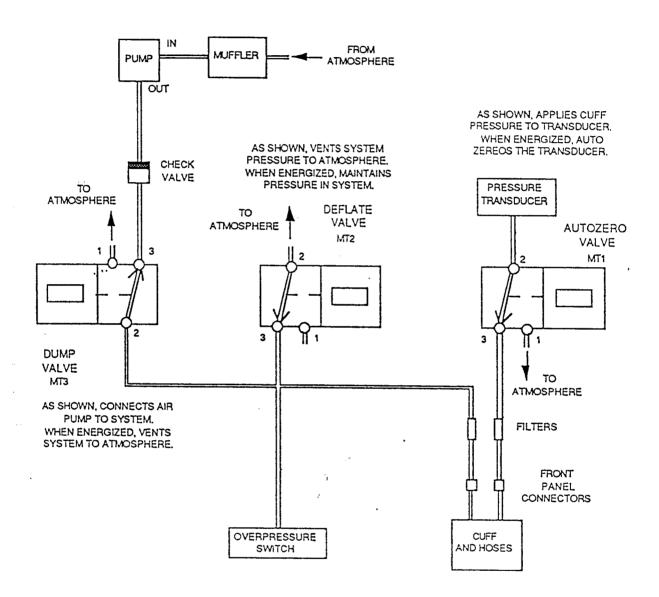

The pneumatics system (Figure 2-2) provides air pressure for the NIBP cuff, manifolding for control of the cuff pressure, and an overpressure signal sent to the system processor in the event pressure exceeds about 300 mm Hg. The system comprises an air pump, check valve, overpressure switch, power control circuit, and three solenoid-operated pneumatic valves. The pneumatics board provides control of the pneumatic pump in accordance with commands received from the system processor.

Figure 2-2. Pneumatics System Simplified Schematic

The rotary-driven diaphragm pneumatic pump is operated by pulse width-modulated dc voltages supplied by the interface circuit. The pump is mounted within a reinforced-plastic air pressure storage vessel. Air from the pump output is routed to the inflate valve port. It is then ported to the cuff output manifold.

FO-5 is a simplified diagram of the pneumatics system control circuits. The pump on command from the system processor is processed by logic U2, U3. The logic turns on Q2 to activate the pump. The pump enable signal is also applied to the fan circuit to prevent excessive power supply loading by disabling the fan until pump operation ceases.

The normally deenergized Zero valve MT1 allows cuff pressure to be applied to the NIBP sensor. When a command from the system processor is processed by logic circuit U2 and U3, Q3 turns on, energizing MT1 to maintain cuff network pressure while opening the transducer to ambient pressure.

Deflate valve MT2 is normally energized when an enable command from logic U2, U3 turns on Q8 to maintain system pressure in the cuff. When a deflate command from the system processor is processed by logic network U2, U3, the deflate valve deenergizes and ports the cuff network to atmosphere.

The normally deenergized dump valve MT3 connects the air pump to the cuff network. When a dump command from the system processor is processed by logic circuit U2 and U3, Q4 turns on, energizing MT3 to port the network to atmosphere.

If system overpressurization occurs, a signal from closed switch S1 (or S2) is applied to logic U2, U3 via U4-1. The logic then energizes the dump valve and deenergizes the deflate valve. An overpressure signal sent to system processor via J1-13 generates visual and audible overpressure alarms. U2, U3 also turns on Q7 during the overpressure condition to ensure the dump valve is energized if Q4 fails. If excessive current is drawn at any time by the pump, a sense signal from Q2 is applied to U4-2. The resulting input to U4-1 results in the same actions described for an overpressure condition.

After a pump shutdown due to overpressure or overcurrent, logic U2, U3 can be reset by the pneumatic reset signal from the system processor. When a fail safe alarm signal is sent to logic U2, U3 from the system processor, the dump valve is energized, the deflate valve is deenergized, and the pump drive circuit is disabled.

Internal temperature is limited by a fan under the control of Q6, comparator U14-14, and thermistor RT1. If an overtemperature conditions occurs, the second comparator output at U14-13 signals the event via J1-5. Valve sense signals from Q3, Q4, and Q8 are applied to the system processor only for use by the factory during manufacturing tests.

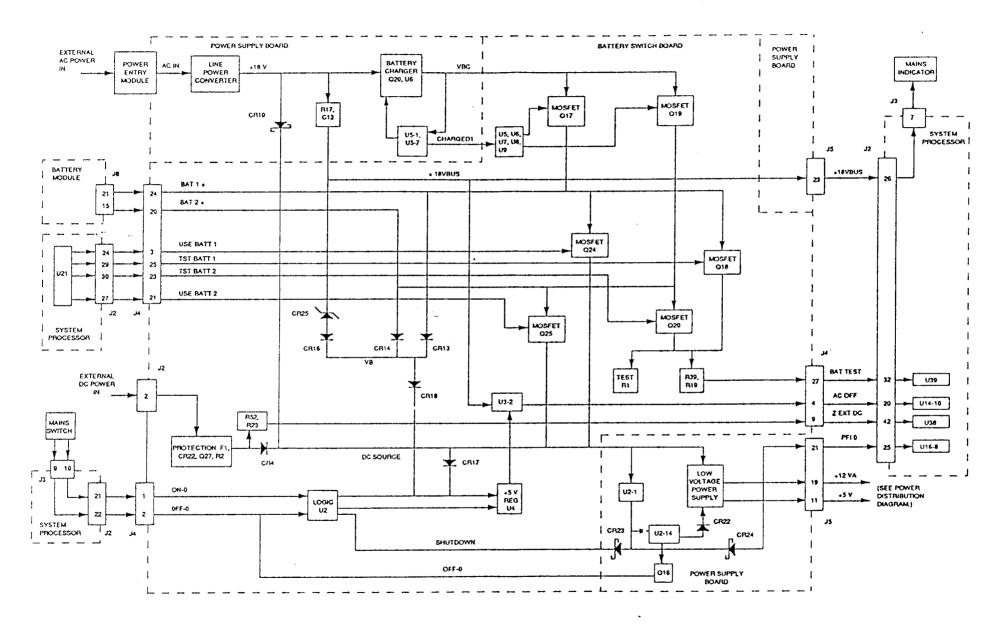

2.3.6 Power Supply

The Monitor power supply system, comprised of components of the power supply board (enclosed in dashed lines) and battery switch board, is illustrated in FO-6. Ac power applied to the line power converter within the power supply board provides a nominal +18 volts dc bus. The presence of the +18 VDC bus is sensed by the system processor via U3-2. The +18 Vdc bus also supplies the voltage that lights the front panel mains indicator.

The power supply DC SOURCE bus can be supplied by external dc power, from either storage battery, or from the power supply board +18 volt bus. An external dc power source is coupled to DC SOURCE by CR4. Overcurrent protection is provided by F1, and CR22, Q27 and R2 are used for overvoltage and reverse-polarity protection. The external dc power input is monitored by the system processor from the voltage drop across R52 and R23. The output from storage battery 1 is switched to DC SOURCE by MOSFET Q24 under command of the USE BATT 1 input from the system processor. The output from storage battery 2 is switched to DC SOURCE by MOSFET Q25 under command of the USE BATT 2 input from the system processor.

The power supply internal VB bus is powered by either storage battery via CR13 and CR14 or from the power supply board +18 volt bus via CR16. Internal +5 volt regulator U4 is powered by the VB bus via CR18 or from the external dc source via CR17.

Battery charger current, derived by Q20, U6 from the +18 Vdc bus, can recharge two storage batteries within 12 hours. Battery charge monitoring and control are provided by a circuit that includes U5-1 and U5-7 on the power supply board and U5, U6, U7, U8, U9 on the battery switch board. MOSFET Q17 applies charging current to storage battery 1, and MOSFET Q19 applies charging current to storage battery 2. The battery charge can be maintained indefinitely without damage to the batteries as long as the Monitor is connected (either switched on or off) to the ac power source.

Storage battery 1 is switched to the test load resistor R1, the equivalent to powering the pneumatic pump motor, by MOSFET Q18 under command of the TST BATT 1 input from the system processor. Storage battery 2 is switched to R1 by MOSFET switch Q20 under command of the TST BATT 2 input from the system processor. Battery test load current is monitored by the system processor from the voltage drop across R39 and R19.

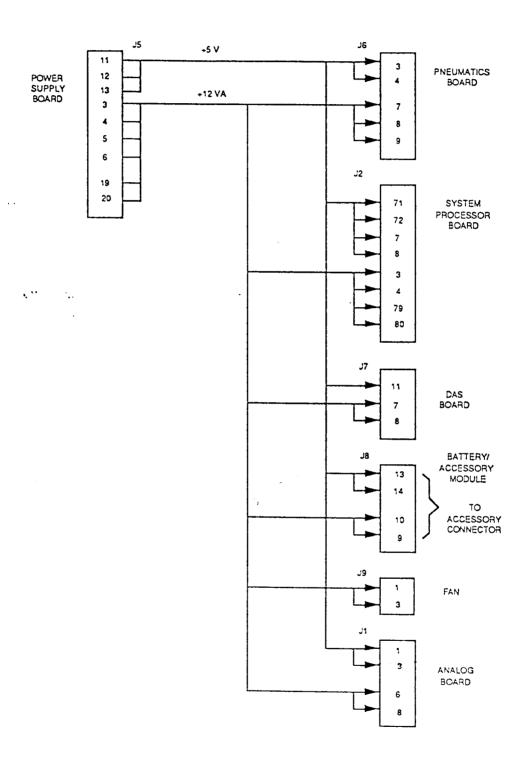

Figure 2-3. Power Distribution Diagram

The low voltage power supply provides regulated +12 V and +5 V outputs to the power distribution system from the DC SOURCE bus. Power distribution within the Monitor is shown in Figure 2-3. An additional power source of -12 Vdc to the system processor from the analog board is described in paragraph 2.3.3.

Power supply on/off control is provided by logic circuit U2, which receives set/clear commands from the front panel mains switch. The logic circuit controls battery switch board operation by commands to the internal +5 Vdc voltage regulator, and applies a shutdown signal to the distribution power supply within the power supply board via U2-14. The shutdown signal is also sensed by the system processor via CR24. A signal from Q16 also switches logic U2 to off to prevent a weak battery from cycling power on until the mains switch is again pressed on.

#### 2.4 SCHEMATIC DESCRIPTIONS

A detailed circuit description of each of the main circuit board assemblies is provided by the following paragraphs.

2.4.1 System Processor Board

The system processor board circuits are shown on schematic SC315-332 contained in Section 4. The system processor is based on Motorola MC68302 Integrated Multiprotocol Processor U41. The 68302 includes a 68000 microprocessor core, a systems integration block, and a communications processor. The 68000 processor core is a low power HCMOS implementation of the MC68000. The system integration block consists of a DMA channel, an interrupt controller, two parallel I/O ports, 1152 bytes of dual port static RAM, three programmable timers, four chip select signals with wait state generation logic, and a clock generator. The communications processor consists of a RISC controller, three serial communications controllers which support UART, HDCL/SDCL, BISYNC, and DDCMP protocols, a synchronous communication channel, and six DMA channels.

The system clock is generated by 16.000 Mhz crystal Y1 and the 68302 internal clock generation circuitry. The clock signal is available at CLKOUT (U41-98) and at test point TP3. Reset signal generation is provided by MAX695 supervisor circuit U40. Its low true output RESET-0 (U40-15) is inverted with one section of 74HC04 U14, then inverted again with two sections of 74HC03 open drain NAND gate U13. The outputs of these NAND gates are connected to RESET-0 (U41-92) and HALT-0 (U41-91) of the 68302. The MAX695 asserts RESET-0 for a minimum of 140 milliseconds after +5V reaches 4.75 V on power up. SYS\_RESET-0 is connected to J2 at pin 60.

The IDMA channel is configured for externally-requested transfers to and from the 63484 graphics controller U31. The control signals DMA request [DREQ-0] (U41-69), DMA acknowledge [DACK-0] (U41-70), and DMA done [DONE-0] (U41-71) are connected to similar pins on the graphic controller.

Four programmable chip signals are available on the 68302. Each has selectable base address, block size, read only, write only, or read-write options, and DTACK/wait state generation. CS0-0 (U41-128) is used to select the program memory EPROM U36 (ROMCS-0). It must be configured for read only operation, and internal DTACK generation. One wait state is required with 150 nsec EPROMs. CS1-0 (U41-127) selects the static RAM (RAMCS-0). It must be configured for read-write operation, and internal DTACK generation. No wait states are required for 85 nsec RAM devices. CS2-0 selects the graphics controller (ACRTCCS-0). It must be configured for read-write operation and external DTACK generation. CS3-0 (U41-126) is used to select IO device address space. It receives additional decoding with 74HC138 U19 and address signals A12, A13, and A14 to provide eight chip selects in 4K byte blocks. CS3-0 must be configured for read-write operation with internal DTACK generation and two wait states.

The interrupt controller is configured to accept requests from internal (on-chip) and external sources. Internal sources are the communication processor and its DMA channels, the IDMA channel, and the internal timers. The external sources are VSYNC-0 and ACRTCIRQ-0 from the graphics subsystem, BPRT\_SYNC-0 from the printer interface, and the power fail signal BPFI-0. Full priority control and vector generation are available in the interrupt controller.

The three serial channels of the 68302 communications processor are all used in UART (asynchronous) mode. Channel one is connected through inverting HC buffers to the host communications connector J4. Bidirectional serial data (RXD1, TXD1) and control signals (CD1,CTS1-0, RTS1-0) are available. Channel two transmit and receive data signals are connected through 74HC541 buffer U30 to the printer via mother board connector J2. Serial transmit and receive communications with the DAS subsystem using channel 3 are also buffered by U30.

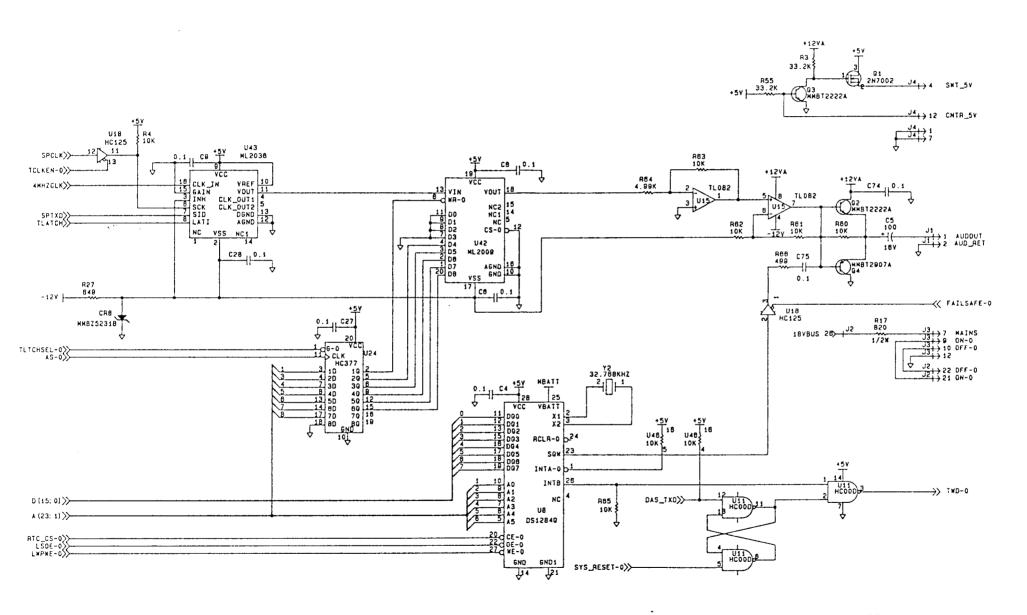

## 2.4.1.1 Failsafe Logic

A latch for the failsafe signal is formed by cross-coupled NAND gates (U13). These devices are open drain, and both their ouputs are pulled up to +5V with 10k ohm resistors of network U45. The active low output of the latch (FAILSAFE-0) is available at J2-17. The latch is cleared by asserting SYS-RESET-0, and set by a low pulse from either the 68302 internal watchdog timer signal WDOG-0 (U41-117) or the gated clock calendar DS1284 TWD-0. WDOG-0 is an open drain output, and is pulled to +5V with a 10k ohm resistor in network U26. The watchdog timer output from DS1284 clock calendar INTB (U8-26) is gated with the Q-0 output of cross-coupled NAND latch U11 to generate TWD-0. This latch is cleared by SYS\_RESET-0 and set by DAS\_TXD, preventing the DS1284 from setting the failsafe latch until the first serial transmission is sent to the DAS subsystem. The WDOG-0 and TWD-0 signals are logically ORed using 74HC08 U16.

When FAILSAFE-0 is asserted, 74HC125 tri-state buffer U18 is enabled, allowing the 1kHz square wave from the DS1284 clock calendar (U8-23) to be driven through 10k ohm resistor R65 into the input of TLM082 audio amplifier U15, producing an audible warning.

FAILSAFE-0 is also an input to ZDEAMANB pin U9-4 of the ACRTC support gate arrray. When asserted, output clock Z115KHZ (U9-68) is disabled, and all serial video data is output on ZPIXDAT (U9-65) following the sixteenth ZPIXHSB (horizontal sync) pulse after the rising edge of ZPIXVSB (vertical sync) is logic zero. This blanks the display except for the top sixteen rows.

#### 2.4.1.2 Read-Only Memory

Program storage consists of a single socket (U36) for wordwide (16 bit) EPROM or PROM devices. The device supports 1MEG (64Kx16), 2MEG (128Kx16), or 4MEG (256Kx16) devices. Chip select is provided by ROMCS-0 (U41-128). This output from the 68302 programmble chip select logic should be configured for base address = 0, read only operation, with the block size set to the corresponding device size. With 150 nsec access time EPROM/PROMs, one-wait state operation is possible. With 100 nsec or faster parts, the system can operate with zerowait states. The OE-0 signal at U36 is generated by ORing of LDS-0 and UDS-0 using 74HC08 U10. Note that the chip select and output enable logic is not fully decoded with respect to read/write external to the 68302. Therefore, unless the 68302 is programmed for read-only operation, a write to the EPROM/PROM address space will cause data bus contention.

## 2.4.1.3 Read/Write Memory

256K bytes of battery-backed read write memory are provided. 128K-by-eight low power static RAM devices U32 and U33 are organized as 128K-by-sixteen bits. U32 contains the upper bits (D8-D15) and U33 contains the lower bits (D0-D7). The RAM is powered by +5V2, provided by the +5V logic rail or the lithium battery voltage, whichever is greater. +5V2 is selected by MAX695 processor supervisor U40-2.

Chip select for the RAM devices is generated by ANDing 68302 programmable chip select logic output RAMCS-0 (U41-127) with MAX695 output WPCE-0 (U40-12) using 74AC32 U2. WPCE-0 goes low only when +5V is greater than +4.65V, thus providing protection against writes to the RAM during power up and down transitions. 74AC32 AND gate U2 is powered by +5V2 to assure minimum battery consumption by driving CS1-0 (U32-22, U33-22) to within 0.1V of +5V2 during power off.

Output enable for U32 is generated by ANDing UDS-0 with the inverted R~W-0 (74HC04, U14) using one section of 74AC32 U5. Output enable for U33 is similar, ANDing LDS-0 with the inverted R~W-0 using one section of 74AC32 U3. Write enable for U32 is generated by ANDing UDS-0 with the R~W-0 using one section of 74AC32 U5. Write enable for U33 is similar, ANDing LDS-0 with R~W-0 using one section of 74AC32 U3.

#### 2.4.1.4 Serial EEPROM

93C46 serial EEPROM U1 provides 1024 bits of non-volatile memory organized as 64 sixteen-bit words. Interface to the 68302 is via the Serial Communication Port (SCP) in the communication processor. The SCP is a three-wire synchronous interface, providing receive data, transmit data, and clock signals.

The EEPROM is selected by asserting output Q0 of 74HC259 bit addressable latch U20-4. Data and instructions are clocked into the EEPROM DI pin (U1-3) on the rising edge of EECLK (U1-2). Data and status information is clocked into the SCP on the falling edge of EECLK. The maximum bit rate for the EEPROM is 700kHz.

### 2.4.1.5 Analog Input Subsystem

A sixteen channel, 12 bit analog input subsystem is based on MAX172 successive-approximation analog-to-digital converter (ADC) U37. The ADC includes on chip voltage reference generation (-5.25V), a 0 to +5V input range. (1 LSB = 1.22 MV) and 13 microsecond maximum conversion time. The 1 MHz conversion clock is generated by the graphics support gate array (U9-31) by dividing down the system clock. The digital output of the MAX172 is isolated from the processor data bus by 74HC541 tri-state buffers U29 and U47. This isolation decreases the coupling of high speed bus digital noise into the conversion circuits. A conversion is started, and the previous result driven onto the data bus by reading address CS3 + 0x2000. The end of a conversion is signalled by the negating of low true BUSY-0 (U37-22), which is connected to Port A bit 7 of processor U41.

MAX358 eight-to-one analog multiplexers U38 and U39 are joined to create a 16-to-one multiplexer. Analog channel selection is controlled by latched address bus signals A3 thru A6 using 74HC377 latch U25. Latched A6 is connected directly to the OUTPUT ENABLE pin of U38, and through 74HC04 inverter U14 to the OUTPUT ENABLE pin of U39. This establishes U39 as the lower eight channels, and U38 as the higher eight. Channel selection within each device is controlled by latched A3, A4, and A5. Latch U25 is accessed by reading address CS3 +0x3000+ (valid select data).

Multiplexor settle time to 12-bit accuracy is 3.5 microseconds. The MAX358 is guaranteed to have break-before-make switch action within each device. However, feedthrough may occur when a new channel is selected from the other device.

The outputs of the two MAX358s are connected to the input of SHC298 sample-and-hold amplifier U44. The input signal is connected to 1000 pF capacitor C19 when CONT\_INP (U41-8) is logic high (SAMPLE), and disconnected when CONT\_INP is low (HOLD). Acquisition time to 12-bit accuracy is 10 microseconds maximum. CONT\_INP is connected to latched address signal A2 via latch U25. The OUTPUT (U44-5) of the SHC298 is connected to the analog input (U32-1) of converter MAX172.

#### 2.4.1.6 Graphics Subsystem

The graphics subsystem is designed to drive a 320-by-256 monochromatic, electroluminescent (EL) display panel. The subsystem consists of the HD63484 graphics controller, a logic support gate array, video memory, and support buffers and logic.

HD63484 advanced CRT controller (ACRTC) U31 offloads from the system processor the tasks of graphics and character generation and control of the display device. The 68302 communicates with either the ACRTC (using normal bus cycles) or with the IDMA channel. OR gates of 74AC32 U4 and flipflop 74AC74 U6 decode chip select logic for the normal and DMA interface.

ELVLSI logic support gate array U9 is a CMOS ASIC that decodes ACRTC to video memory accesses and serializes graphics bit data for transfer to the EL panel. In addition, it provides display blanking during system failures and division of the system clock.

The video memory consists of two 128k-by-8 bit static RAMs organized as a 128k-by-16 bits wide. Interface signals to the EL panel are located at connector J5. They are buffered version of VIDEO\_DATA, VIDEO\_CLK, VIDEO\_HS (Horizontal Sync), and VIDEO\_VS (Vertical Sync).

#### 2.4.1.7 Realtime Clock

A battery backed DS1284 realtime clock device U8 provides time of day and calendar information. The device is powered from the logic power rail when available, or from 3.7V (nominal) lithium battery B1 when the system is powered down. The DS1284 includes internal oscillator circuitry which provides a stable timebase using 32768 Hz crystal Y2. The DS1284 byte wide registers are located at odd bytes starting at CS3+0x4000. Write protection of these registers during power transitions uses the WPCE-0 output from MAX695 processor supervisor U40, gated with LDS-0 and R~W-0 using always-powered 74AC32 U2. The watchdog alarm features are used in the failsafe logic circuits described above.

# 2.4.1.8 Audio Subsystem

An audio subsystem is included to generate sound for rate detection, key annunciation, and alarms. It consists of an programmable sinewave generator, an logrithmic attenuator amplifier circuit, an output amplifier, and an enable circuit. It is a single channel system designed to drive an 8-ohm speaker.

ML2036 programmable sinewave generator U43 produces a sinewave output of approximately 5 volts peak to peak centered on +5V\_RET. The output frequency is the programmed (serial) 16 bit data word divided by four. The ML2036 uses a 4 MHz clock, which is the 16 MHz system clock divided by four in graphics support gate array U9. The ML2036 is interfaced to the 68302 via the write only Serial Communication Port (SCP) and two digital control signals. TCLKEN-0 controls the synchronous clock from the 68302 (U41-77). It is an output from 74HC259 addressable latch U22. When asserted, it turns on 74HC125 tri-state buffer U18, which enables the clock signal to the ML2036 SCK input (U43-6). The output of the 74HC125 buffer is pulled to the logic rail through 10k ohm resistor R4. Serial data is clocked into the ML2036 on rising edges of SCK: TLATCH controls the ML2036 data latch. It must be high during serial data transmission, and latches the data on its falling edge. TLATCH is an output of 74HC259 addressable latch U22. Because the 68302 SCP is an 8-bit device, two writes are required to set the frequency. The ML2036 expects the data to be shifted least significant bit

ML2009 logarithmic attenuator/gain amplifier U42 provides volume control for the audio system. It provides up to 44 dB of dynamic range with sixteen levels each of attenuation and gain. The output level is selected by a 5-bit word using 74HC377 latch U24. The input to the latch is the system address bus, where A7 selects attenuate (logic hi) or gain (logic low), A3 through A6 select the sixteen levels, and A1 acts as the write strobe (WR-0). Multiple writes to the latch (located at CS3+ 0x6000) are required for proper programming, first with A1 low, then with A1 high.

The output amplifier consists of two stages of TL082 op amp U15 and discrete transistor pair Q2 and Q4. The ML2009 output feeds the first stage of U15 in a inverting gain-of-2 configuration. The second U15 stage is a unity gain stage with a 5 volt offset added. The output of the second stage drives the bases of transistors Q2 and Q4, which are in a push-pull arrangement. 10 k ohm resistor R60 provides feedthrough near the switch point to reduce distortion.

The bases of Q2 and Q4 are also driven by the output of 74HC125 tri-state buffer U18 to emit an audible alarm if a failsafe occurs. The emitters of the Q2/Q4 pair are coupled to speaker connector J1 through 100 microfarad capacitor C5. An audio enable circuit controlled by digital output Q7 of 74HC259 addressable latch U20 switches the AUD\_RET (J1-2) to +5V\_RET when N-channel MOSFET MTD5N05 is turned on.

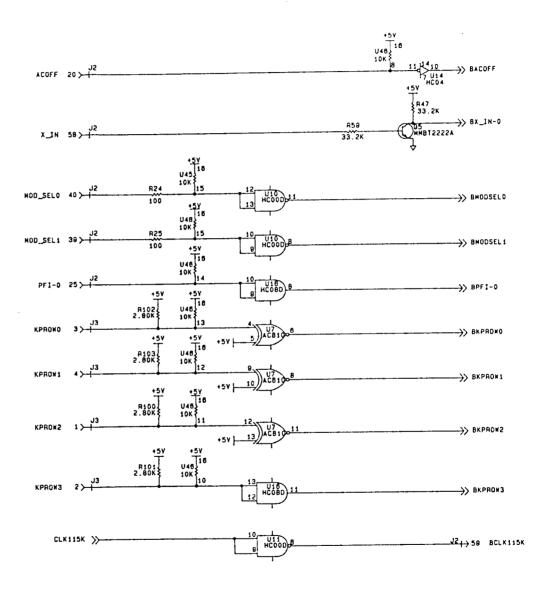

#### 2.4.1.9 Keypad Interface

An interface to a matrix-encoded keypad is provided at connector J3. The circuit consists of three output strobe signals and four input sense signals. The strobe signals (KBCOL0,KBCOL1, and KBCOL2) are active low outputs from 74HC259 addressable latch U20. These outputs are series diode protected to eliminate shorts during multiple key closures. The sense signals (KPROW0, KPROW1, KPROW2, and KPROW3) are pulled to the logic rail through 2.8k ohm resistors and buffered with three sections of 74AC810 U7 and one section of 74HC08 U16. The non-inverting output of these buffers (BKPROW0, BKPROW1, BKPROW2, and BKPROW3) connect to digital I/O port B bits 0 through 3 of the 68302 microprocessor.

## 2.4.1.10 Digital Inputs

All digital inputs are read by bits in ports A or B on the 68302. These inputs are isolated by buffers or logic gates.

#### 2.4.1.11 Digital Output Ports

Two octal output ports are provided that interface to a four channel DAC and two addressable latches on the analog board, but also can be used for general purpose output. The lower 8-bit system data bus is latched by 74HC377 U26 during writes to CS3 +0x7700. The outputs of the latch are available as PD0 - PD7 at pins 50 through 57 of connector J2.

Eight bits of the address bus are latched by 74HC377 U27 during writes to CS3+ 0x7000 +value. The low order address values (A1, A3 through A6, A8 through A10) are dependent on the desired output value. DAC\_STB-0 (latched A1) is at J2-43. LATCH\_DATA (latched A3) is at J2-47. CHSEL0 (latched A4) is at J2-44. CHSEL1 (latched A5) is at J2-45. CHSEL2 (latched A6) is at J2-46. POLATCHSEL-0 (latched A8) is at J2-48. BPLATCHSEL-0 (latched A9) is at J2-49. X\_OUT (latched A10) is at J2-38.

74HC259 bit addressable latch U21 provides eight digital outputs to connector J2. The device is selected by byte reads to even addresses at CS3+ value, with A3, A4, and A5 selecting the output bit and A1 providing the data. 74HC259 latch U20 is addressed like U21, except using odd addresses at CS3+ 0x1000 +value. It provides three outputs to connector J2, plus the three keypad strobes described above. U22 is an additional 74HC259 latch addressed in a similar manner, with its base at CS3+0x1000 +value using even addresses.

# 2.4.2 DAS Board

The DAS board circuits (Models 8720 and 8710 only) are shown on schematic SC315-370 contained in Section 4. The DAS board contains components of the Data Acquisition System (DAS), including the following subsystems:

The Microprocessor (DAS CPU), Opto-isolators, and control logic

The Analog to Digital Converter (ADC) and multiplexer

The ECG channel and lead switching

The two Invasive Blood Pressure (IBP) channels

The temperature channel

The isolated power supply

The physiological signals are acquired, amplified, and filtered, after which they are converted to digital values. Further signal processing occurs on the digital values to perform QRS detection, pacemaker spike rejection, and further conditioning of the IBP and temperature signals. The processed data is then sent to the Monitor system processor along with DAS status and error conditions. DAS receives commands from the Monitor system processor to configure the ECG leads, calibrate the pressure channels, check the temperature channel, and initialize the DAS system. For patient safety, the entire DAS system is electrically isolated from earth ground by the isolated power supply and isolated serial communications port.

# 2.4.2.1 DAS CPU, Opto-Isolators, and Control Logic

The DAS CPU and its associated control logic are responsible for the overall control and operation of the DAS. DAS CPU U1 is a single chip microcomputer (HD63B03Y) with onboard parallel and serial ports and 256 bytes of RAM.

The parallel ports are bidirectional. Initially configured as input on reset, each bit can later be configured as either an input or an output. The parallel ports of the DAS CPU are used to control the ECG lead switching, ECG fast charge, multiplexer channel selection, IBP channel testing, and the temperature channel switching. Additionally, inputs from the various power supplies are monitored for power supply faults. ADC interrupts, status information, and ADC calibration control are also handled through the parallel ports. Refer to 2.4.2.8 for a full definition of the parallel port assignments.

Communications with the Monitor system processor is through the serial communications port, paragraph 2.4.2.8. Isolation for the IO channels is provided by opto-isolators U5 and U6. Q9 supplies the LED current for the transmit opto-isolator.

Control logic U3 and U4 provide for DAS CPU address space mapping and communications baud rate clock generation. Both the address line A15 and the DAS CPU E clock must be high to enable EPROM U2; thus, the EPROM is addressed from 8000 hex through FFFF hex. Test point TP1, if grounded, disables the onboard EPROM, thereby allowing an external memory to access the bus from the same address space. In the ADC mapping logic, address line A15 must be low and address line A14 must be high to select the ADC. Thus the ADC is mapped at addresses 4000 hex through 7FFF hex. The DAS CPU E clock is added to deglitch the output.

U4 is a standard D type flip-flop configured as a divide-by-two counter. The DAS CPU E clock is divided from 2 MHz to 1 MHz by this circuit. The output of the clock generator is applied to the external baud rate clock input of the DAS CPU. The DAS CPU uses this as a 16X baud rate clock, giving a serial data rate of 62.5 K baud.

On power up, or if the digital supply ever goes out of tolerance, reset generator U16 will cause a DAS CPU reset. Once proper operating conditions are detected, the reset is removed after a pre set delay. A reset can be generated manually by grounding RESET IN test point TP9.

# 2.4.2.2 Analog to Digital Converter and Multiplexer

Analog-to-digital converter U7 has a resolution of 12 bits plus sign and has an onboard sample and hold amplifier. Other features of the ADC include automatic calibration and automatic zeroing of the input. In the 8700 DAS all conversions are done with an auto zero cycle. To ensure conversion accuracy over temperature, an auto calibration cycle is executed once for each pass through the MUX channels. The ADC presents the 13-bit data in two bytes, high byte first and sign extended.

The ADC clock source is the 2 MHz DAS CPU E clock. For each conversion, the ADC requires 26 clock cycles to execute an auto zero, seven cycles to acquire the signal, and 27 cycles to convert the sample. This results in an overall conversion time of 30 microseconds.

To protect the ADC input from overvoltage, a clamping network is used between multiplexer U9 and buffer amp U29. Series resistor R1 protects the ADC input from overcurrent should the buffer output go high for any reason.

The reference voltage for the ADC comes from +5V linear regulator U12. Since ratiometric techniques are used for all precision measurements in the DAS, the absolute value of the ADC reference voltage is not critical. An error output signals the DAS CPU if a fault is detected in the ADC reference.

U9 is a standard eight-channel single-ended analog multiplexer. The desired signal is selected by the MUX control lines MUX0 through MUX2. Multiplexer channel assignments are listed in paragraph 2.4.2.8.

# 2.4.2.3 ECG Channel and Lead Switching

The ECG channel consists of an input protection network, lead switch circuit, instrumentation amplifier (IA), lead fail detection circuits, common mode nulling loop, high-pass filter with a fast charge setting, and a fourth-order low pass filter. Display channel gain is 800 with a bandwidth of .05 to 40 Hz.

The input protection network consists of high voltage series resistors, neon surge suppressors, high value series resistors, filter capacitors, and slew leakage diodes. The neon surge suppressors protect the input from defibrillator voltages by turning on at 60 to 90 volts. The power resistors limit the amount of defibrillator energy lost to the monitor. A resistor is placed in series with the ECG shield terminal to limit currents induced in the ground plane during defibrillation. The high value series resistors, in concert with the filter capacitors, form a passive low pass filter to reduce electro-surgical noise. The last stage of protection is the back-to-back diodes, which limit the voltage appearing at that point to a bit more than 5V.